상위 질문

타임라인

채팅

관점

클럭 발생기

위키백과, 무료 백과사전

Remove ads

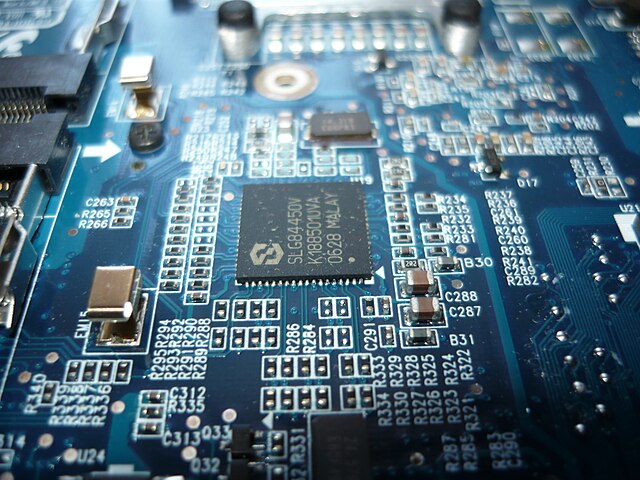

클럭 발생기(Clock generator)는 회로 작동을 동기화하는 데 사용되는 클럭 신호를 생성하는 전자 발진기이다. 출력 클럭 신호는 단순한 대칭형 방형파에서부터 더 복잡한 배열에 이르기까지 다양할 수 있다. 모든 클럭 발생기가 공유하는 기본 부품은 공진 회로와 앰프이다.

공진 회로는 일반적으로 석영 압전기 진동자이지만, 더 간단한 LC 회로나 심지어 RC 회로도 사용될 수 있다.

앰프 회로는 일반적으로 발진기의 신호를 반전시키고 그 일부를 발진기로 다시 공급하여 발진을 유지한다.

발생기에는 기본 신호를 수정하기 위한 추가 섹션이 있을 수 있다. 예를 들어, 인텔 8088은 2/3 듀티 사이클 클럭을 사용했는데, 이는 클럭 발생기가 원시 발진기에 전형적인 50/50 듀티 사이클을 변환하는 로직을 통합해야 했다.

이러한 다른 선택적 섹션에는 주파수 분배기 또는 클럭 승수 섹션이 포함된다. 프로그래밍 가능한 클럭 발생기는 분배기 또는 승수에 사용되는 숫자를 변경할 수 있도록 하여 하드웨어를 수정하지 않고도 다양한 출력 주파수 중 하나를 선택할 수 있게 한다.

메인보드의 클럭 발생기는 컴퓨터 애호가들에 의해 CPU, FSB, GPU 또는 RAM의 속도를 제어하기 위해 자주 변경된다. 일반적으로 프로그래밍 가능한 클럭 발생기는 부팅 시 바이오스에 의해 선택된 값으로 설정된다. 일부 시스템에는 클럭 발생기를 자주 다시 프로그래밍하는 동적 주파수 스케일링이 있다.

Remove ads

타이밍-신호 발생기 (TSG)

TSG는 서비스 제공자 네트워크 전반에 걸쳐 사용되는 시계이며, 종종 중앙 사무실을 위한 빌딩 통합 타이밍 공급(BITS)으로 사용된다.

디지털 교환 시스템 및 일부 전송 시스템(예: SONET, RREX, LUBI)은 손상을 방지하기 위해 안정적이고 고품질의 동기화(또는 타이밍)에 의존한다. 이를 제공하기 위해 대부분의 서비스 제공자는 스트레이텀 계층을 기반으로 하는 사무실 간 동기화 분배 네트워크를 사용하고 사무실 내 동기화 요구 사항을 충족하기 위해 BITS 개념을 구현한다.

TSG는 입력 타이밍 참조 신호를 수신하고 출력 타이밍 참조 신호를 생성하는 클럭 장비이다. 입력 참조 신호는 DS1 또는 복합 클럭(CC) 신호일 수 있으며, 출력 신호도 DS1 또는 CC 신호(또는 둘 다)일 수 있다. TSG는 아래 나열된 6가지 구성 요소로 구성된다.

- DS1 또는 CC 입력 신호를 수신하는 입력 타이밍 인터페이스

- 출력 타이밍 분배 구성 요소에서 사용되는 타이밍 신호를 생성하는 타이밍 생성 구성 요소

- 타이밍 생성 구성 요소의 타이밍 신호를 활용하여 여러 DS1 및 CC 출력 신호를 생성하는 출력 타이밍 분배 구성 요소

- 입력 신호의 타이밍 특성을 모니터링하는 성능 모니터링(PM) 구성 요소

- 중앙 사무실(CO) 경보 모니터링 시스템에 연결되는 경보 인터페이스

- 현지 기술자 사용 및 원격 운영 시스템과의 통신을 위한 운영 인터페이스

Remove ads

같이 보기

외부 링크

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads