Top Qs

Linha do tempo

Chat

Contexto

Computação paralela

Da Wikipédia, a enciclopédia livre

Remove ads

Computação paralela é um tipo de computação em que muitos cálculos ou processos são realizados simultaneamente.[1] Problemas de grande porte muitas vezes podem ser divididos em partes menores, que podem então ser solucionadas ao mesmo tempo. Existem várias formas de computação paralela: Paralelismo em nível de bit, Paralelismo em nível de instrução, Paralelismo de dados e Paralelismo de tarefas. O paralelismo há muito é empregado em computação de alto desempenho, mas ganhou interesse mais amplo devido às limitações físicas que impedem o escalonamento de frequência.[2] Como o consumo de energia (e consequentemente a geração de calor) pelos computadores se tornou uma preocupação nos últimos anos,[3] a computação paralela tornou-se o paradigma dominante em arquitetura de computadores, principalmente na forma de processadores multinúcleo.[4]

Em ciência da computação, paralelismo e concorrência são duas coisas diferentes: um programa paralelo utiliza múltiplos núcleos de CPU, cada núcleo executando uma tarefa de forma independente. Por outro lado, concorrência possibilita que um programa lide com várias tarefas mesmo em um único núcleo de CPU; o núcleo alterna entre tarefas (isto é, threads) sem necessariamente concluir cada uma. Um programa pode apresentar características de paralelismo, de concorrência, ambos ou nenhum dos dois.[5]

Computadores paralelos podem ser classificados conforme o nível em que o hardware suporta paralelismo: computadores multinúcleo e multiprocessadores simétricos possuem vários elementos de processamento numa única máquina, enquanto clusters, MPPs e grids usam múltiplos computadores para trabalhar na mesma tarefa. Arquiteturas especializadas são às vezes usadas juntamente com processadores tradicionais para acelerar tarefas específicas.

Em alguns casos o paralelismo é transparente ao programador, como no paralelismo em nível de bit ou em nível de instrução, mas algoritmos paralelos explícitos, especialmente os que usam concorrência, são mais difíceis de escrever do que algoritmos sequenciais,[6] pois a concorrência introduz várias novas classes de potenciais bugs, sendo as condições de corrida as mais comuns. Comunicação e sincronização entre subtarefas são frequentemente alguns dos maiores obstáculos para obter desempenho ótimo.

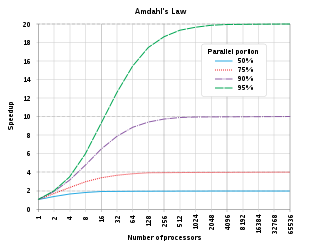

Um limite teórico para o aceleração de um programa pela paralelização é dado pela Lei de Amdahl, que afirma que ela é limitada pela fração de tempo que pode ser paralelizada.

Remove ads

Antecedentes

Resumir

Perspectiva

Tradicionalmente, software de computador era escrito para computação serial. Para resolver um problema, constrói-se um algoritmo e o implementa como um fluxo serial de instruções. Essas instruções são executadas em uma unidade central de processamento de um único computador. Apenas uma instrução é executada por vez — após sua conclusão, a próxima é executada.[7]

Por outro lado, a computação paralela usa múltiplos elementos de processamento simultaneamente para resolver um problema. Isso é feito dividindo o problema em partes independentes, de modo que cada elemento execute sua parte do algoritmo ao mesmo tempo que os demais. Os elementos podem incluir um único computador com vários processadores, vários computadores em rede, hardware especializado ou qualquer combinação.[7] Historicamente, a computação paralela era usada em aplicações científicas e simulações, particularmente nas ciências naturais e de engenharia, como meteorologia. Isso levou ao desenvolvimento de hardware e software paralelos, bem como à computação de alto desempenho.[8]

O escalonamento de frequência foi o principal fator de melhoria em desempenho de computador de meados dos anos 1980 até 2004. O tempo de execução de um programa é o número de instruções multiplicado pelo tempo médio por instrução. Aumentar a frequência do relógio reduz esse tempo médio, diminuindo o tempo total de programas CPU-bound.[9] Contudo, o consumo de energia ‹P› de um chip é dado por ‹P› = ‹C› × ‹V›² × ‹F›, onde ‹C› é a capacitância comutada (proporcional ao número de transistores ativos), ‹V› é a tensão e ‹F› é a frequência do relógio. Aumentos em ‹F› elevam o consumo. Esse problema levou ao cancelamento dos processadores Tejas and Jayhawk da Intel em 8 de maio de 2004, marcando o fim do escalonamento de frequência como paradigma dominante.[10]

Para mitigar consumo e calor, fabricantes de CPU começaram a produzir processadores energeticamente eficientes com múltiplos núcleos. Cada núcleo é independente e acessa a mesma memória concorrentemente. Processadores multinúcleo trouxeram a computação paralela a computadores de mesa. Em 2012, processadores quad-core tornaram-se padrão em desktops, enquanto servidores já possuíam 10+ núcleos. Até 2023, alguns chegavam a mais de cem núcleos, inclusive com núcleos de desempenho e eficiência (como ARM big.LITTLE).[11] Pela Lei de Moore, prevê-se que o número de núcleos dobrará a cada 18–24 meses.

Um sistema operacional pode distribuir tarefas em múltiplos núcleos. Contudo, para que software serial aproveite totalmente o multicore, o programador deve reestruturar e paralelizar o código. O ganho de desempenho não virá mais do aumento de frequência, mas da paralelização do software.[12]

Leis relevantes

Artigo principal: Lei de Amdahl

Ideally, o Speedup da paralelização seria linear — dobrar o número de elementos de processamento reduziria o tempo pela metade; dobrar novamente, reduziria pela metade de novo. Porém, raros algoritmos alcançam esse ganho ótimo. A maioria tem aceleração quase linear para poucos elementos, mas estagna com muitos.

O ganho potencial máximo de um sistema é calculado pela Lei de Amdahl.[13] A Lei de Amdahl indica que o melhor desempenho é alcançado equilibrando aprimoramentos em componentes paralelizáveis e não paralelizáveis, e mostra retornos decrescentes ao adicionar processadores.[14][15]

A Lei de Amdahl tem limitações: assume carga fixa, ignora sobrecargas de comunicação e sincronização, foca no aspecto computacional e negligencia fatores extrínsecos como persistência de dados, E/S e acesso à memória.[16][17][18]

As leis de Gustafson e Lei de Escalabilidade Universal oferecem avaliações mais realistas do desempenho paralelo.[19][20]

Dependências

Compreender dependências de dados é fundamental para algoritmos paralelos. Nenhum programa pode rodar mais rápido que o maior caminho crítico (a longa cadeia de cálculos dependentes), pois cálculos dependentes devem seguir ordem. Mas a maioria dos algoritmos não é apenas uma longa cadeia; há oportunidades de paralelismo.

Sejam Pi e Pj segmentos de programa. As condições de Bernstein definem quando são independentes e podem rodar em paralelo:[21]

Violação de fluxo ocorre na primeira, antidependência na segunda, e dependência de saída na terceira.

Exemplos:

: 1: function Dep(a, b) : 2: c := a * b : 3: d := 3 * c : 4: end function

Aqui, instrução 3 depende de 2 (fluxo), não podendo rodar antes ou em paralelo.

: 1: function NoDep(a, b) : 2: c := a * b : 3: d := 3 * b : 4: e := a + b : 5: end function

Sem dependências, todas podem rodar em paralelo.

Bernstein não permite memória compartilhada; para isso, é preciso impor ordenação entre acessos, como semáforos ou barreiras.[22]

Condições de corrida, exclusão mútua, sincronização e desaceleração paralela

Subtarefas são chamadas threads. Algumas arquiteturas usam fibers ou processes, mas "threads" é o termo genérico.[23] Threads frequentemente precisam de acesso sincronizado a um recurso, como ao atualizar uma variável compartilhada. Sem sincronização, instruções podem ser entrelaçadas de modo incorreto, criando condição de corrida. Exemplo:

Se 1B ocorre entre 1A e 3A, dados incorretos resultam. Usa-se lock para exclusão mútua:

Locks garantem correção, mas podem retardar e afetar confiabilidade.[24]

Bloquear múltiplas variáveis com locks não atômicos pode causar deadlock. Locks atômicos bloqueiam múltiplas variáveis de uma vez, evitando deadlocks.[25]

Muitos programas exigem que threads sincronizem em barreiras, implementadas com locks ou semáforos.[26] Algoritmos lock-free e wait-free evitam locks, mas são difíceis e exigem estruturas de dados especiais.[27]

Nem toda paralelização resulta em aceleração: threads podem gastar mais tempo comunicando ou esperando recursos.[28][29] Quando sobrecarga de comunicação domina, mais threads podem aumentar o tempo — chamado parallel slowdown.[30] Pode ser mitigado por análise e redesenho de software.[31]

Paralelismo de grão fino, grosso e embarassingly parallel

Aplicações são classificadas segundo a frequência de comunicação entre subtarefas. Se precisam se comunicar muitas vezes por segundo, têm paralelismo de grão fino; poucas vezes, grão grosso; raramente, Embarrassingly parallel, as mais fáceis de paralelizar.

Taxonomia de Flynn

Michael J. Flynn criou um dos primeiros sistemas de classificação para computadores e programas, conhecido como Taxonomia de Flynn. Ele classificou conforme o número de fluxos de instruções e dados:

- SISD (Single Instruction, Single Data): programa totalmente sequencial.

- SIMD (Single Instruction, Multiple Data): mesma operação em múltiplos dados, comum em processamento de sinais.

- MISD (Multiple Instruction, Single Data): raro; arquiteturas como systolic array foram propostas mas pouco usadas.

- MIMD (Multiple Instruction, Multiple Data): mais comum em programas paralelos.

Segundo David A. Patterson e John L. Hennessy, "Algumas máquinas são híbridas destas categorias, mas este modelo clássico sobrevive por ser simples, fácil de entender e oferecer uma boa aproximação. É também — talvez por sua compreensão clara — o esquema mais amplamente usado."[32]

Remove ads

Desvantagens

A computação paralela pode gerar grande sobrecarga na mesclagem de dados de múltiplos processos. Especificamente, comunicação e sincronização podem ter custos duas ou mais ordens de magnitude superiores ao processamento em thread única.[33][34][35] Portanto, a melhoria global deve ser cuidadosamente avaliada.

Granularidade

Resumir

Perspectiva

Paralelismo em nível de bit

Do advento da tecnologia VLSI na década de 1970 até cerca de 1986, o aumento de velocidade era obtido dobrando-se o tamanho da palavra de máquina — a quantidade de informação manipulável por ciclo. Aumentar o tamanho da palavra reduz o número de instruções para operações em variáveis maiores. Por exemplo, um processador de 8 bits precisa de duas instruções para somar inteiros de 16 bits, enquanto um de 16 bits faz em uma só.

Microprocessadores de 4 bits foram substituídos por 8, depois 16, depois 32 bits, padrão por duas décadas. Nos anos 2000, x86-64 introduziu processadores de 64 bits.

Paralelismo em nível de instrução

Um programa é um fluxo de instruções. Sem paralelismo em instrução, processadores emitem menos de uma instrução por ciclo (IPC < 1), sendo subescalares. Instruções podem ser reordenadas e agrupadas para execução paralela sem alterar o resultado — paralelismo em nível de instrução. Dominou a arquitetura de meados dos anos 1980 aos 1990.[36]

Processadores modernos têm pipelines de N estágios, podendo ter até N instruções em estágios diferentes, alcançando IPC = 1. Exemplo canônico: RISC de cinco estágios (IF, ID, EX, MEM, WB). O Pentium 4 tinha pipeline de 35 estágios.[37]

Muitos também têm múltiplas unidades de execução, combinadas com pipeline, emitindo >1 instrução por ciclo (IPC > 1). São chamados superscalar. Difere de Processador multinúcleo: as unidades não são núcleos independentes. Instruções só agrupam se não houver dependência de dados. Técnicas comuns: scoreboarding e algoritmo de Tomasulo.

Paralelismo de tarefas

Paralelismo de tarefas significa que cálculos totalmente diferentes podem ocorrer no mesmo ou em diferentes dados.[38] Contrasta com paralelismo de dados, onde o mesmo cálculo é aplicado a diferentes dados. Envolve decompor tarefas em subtarefas, alocando cada uma a um processador, executando-as concorrentemente. Não escala com o tamanho do problema.[39]

Paralelismo em nível de superpalavra

Paralelismo de superpalavra é técnica de vetorização automática baseada em desenrolar laços e vetorização de blocos básicos, explorando paralelismo em código inline, como manipulação de canais de cor ou coordenadas.[40]

Remove ads

Hardware

Resumir

Perspectiva

Memória e comunicação

A memória principal pode ser memória compartilhada (num único espaço de endereçamento), ou memória distribuída.[41] Memória distribuída implica distribuição lógica e física. Memória compartilhada distribuída e virtualização de memória combinam abordagens, com acesso mais rápido à memória local. Em supercomputadores, memória compartilhada distribuída pode usar modelos PGAS. Nós se conectam a um sistema de memória compartilhada externa via interconexão de alta velocidade (ex.: Infiniband), chamado burst buffer, construído com arrays de memória não volátil distribuídos.

Arquiteturas com latência e largura de banda uniformes são UMA; tipicamente memória compartilhada não distribuída. Arquiteturas não-UMA são NUMA, comum em sistemas distribuídos.

Sistemas paralelos usam caches — memórias rápidas próximas ao processador. Coerência de cache é complexa, exigindo técnicas como bus snooping. Sistemas compartilhados escalam pior que distribuídos.[41]

Comunicação entre processadores pode ser via memória compartilhada multiportada, crossbar switch, barramento ou redes de interconexão (estrela, anel, árvore, hipercubo, malha, etc.). Roteamento é necessário para nós não diretamente conectados, especialmente em máquinas multiprocessadas hierárquicas.

Classes de computadores paralelos

Classificação análoga à distância entre nós de computação. Não exclusivas; clusters de SMPs comuns.

Computação multinúcleo

Processador multinúcleo tem vários núcleos no mesmo chip, emitindo instruções de múltiplos fluxos por ciclo, diferentemente de superscalar (múltiplas unidades de execução de um fluxo). Ex.: Cell da IBM, usado no PlayStation 3. Cada núcleo pode ser superscalar.

Multithreading simultâneo (ex: Hyper-Threading) foi forma inicial de pseudo-multinúcleo. Processadores com multithreading concorrente têm múltiplas unidades de execução; multithreading temporal emite uma instrução de múltiplos threads.

Multiprocessamento simétrico

SMP é sistema com vários processadores idênticos compartilhando memória via barramento.[42] Contenção de barramento limita SMPs a ~32 processadores.[43] SMPs são custo-efetivos com caches grandes, desde que haja largura de banda de memória.[42]

Computação distribuída

Computador distribuído conecta elementos por rede. Termos "concorrente", "paralelo" e "distribuído" se sobrepõem.[44][45] Um sistema pode ser paralelo e distribuído simultaneamente.

Clusters

Clusters são grupos de computadores independentes trabalhando juntos, agindo como um só.[46] Máquinas idem facilitam balanceamento de carga. Ex.: cluster Beowulf em COTS com Ethernet.[47] Desenvolvido por Thomas Sterling e Donald Becker. 87% dos Top500 são clusters.[48] Grids tratam problemas embarassingly parallel; clusters modernos lidam com problemas que exigem compartilhamento frequente de dados, requerendo alta largura de banda e baixa latência (ex.: Cray Gemini, InfiniBand, Myrinet, Gigabit Ethernet).

Computação massivamente paralela

MPP é um único sistema com muitos processadores em rede, com interconexão especializada, normalmente >100 CPUs.[49] Cada CPU tem memória e sistema operacional próprios, comunicando-se por interconexão de alta velocidade.[50] Ex.: Blue Gene/L ficou em 5.º no Top500 de junho de 2009.

Computação em grade

Grid computing usa Internet para resolver problemas embarassingly parallel em larga escala. Usa middleware (ex.: BOINC). Computação voluntária aproveita ciclos ociosos.[51]

Cloud computing

A ubiquidade da Internet possibilitou computação em nuvem.

Computadores especializados

Dispositivos especializados para tarefas paralelas específicas.

Computação reconfigurável com FPGA

Computação reconfigurável usa FPGAs como coprocessadores. Programáveis em VHDL[52] ou Verilog.[53] Linguagens C-to-HDL: Mitrion-C, Impulse C, Handel-C. SystemC (C++) serve FPGAs.

AMD abriu HyperTransport a terceiros, viabilizando computação reconfigurável de alto desempenho.[54] Segundo Michael R. D'Amour, "quando entramos na AMD, eles nos chamavam de 'socket stealers'. Agora somos parceiros."[54]

GPGPU

Computação geral em GPUs usa coprocessadores otimizados para gráficos e álgebra linear.[55] Surgiram linguagens e APIs: CUDA, AMD FireStream SDK, BrookGPU, PeakStream, RapidMind. Nvidia Tesla e especificação OpenCL do Khronos Group são suportadas por AMD, Apple, Intel, Nvidia etc.

ASICs

ASICs para aplicações paralelas podem superar CPUs gerais em desempenho, mas exigem máscaras caras (~US$1 mi).[56] Lei de Moore tende a anular ganhos em 1–2 gerações.[54] Apesar de caros e ultrapassados rapidamente, alguns existem, como o MDGRAPE-3 do RIKEN.

Processadores vetoriais

Processador vetorial executa instruções em vetores de dados, contrastando com processadores escalares. Ex.: A = B × C, onde A, B e C são vetores de 64 elementos de ponto flutuante.[57] Flynn SIMD. Cray tornou vetoriais famosos; hoje vetorização está em instruções vetoriais (AltiVec, SSE).

Remove ads

Software

Linguagens de programação paralela

Linguagens, bibliotecas e APIs para programação paralela dividem-se conforme memória: compartilhada, distribuída ou mista. POSIX Threads e OpenMP são populares em memória compartilhada; MPI domina passagem de mensagens.[58] Conceitos como futuro permitem prometer dados entre partes do programa.

Padrões como OpenHMPP oferecem diretivas para offload em aceleradores e otimização de transferência de dados via RPC.

Paralelização automática

Automatizar paralelização por compilador é o "Santo Graal" da computação paralela. Resultados até agora são limitados a classes específicas de algoritmos científicos e numéricos.[59]

Checkpointing de aplicação

Com sistemas maiores, a MTBF cai. Checkpointing tira um "snapshot" da aplicação — alocações e estados — permitindo retomar do último ponto em caso de falha. Muito útil em sistemas paralelos com muitos processadores.[60]

Remove ads

Métodos algorítmicos

Computadores paralelos maiores e mais rápidos permitem resolver problemas antes inviáveis em bioinformática (dobramento de proteínas, análise de sequências) e economia. Problemas comuns incluem:[61]

- Álgebra linear densa

- Álgebra linear esparsa

- Métodos espectrais (p.ex. Cooley–Tukey FFT)

- Problemas de N corpos (p.ex. Barnes–Hut)

- Problemas em grade estruturada (p.ex. Lattice Boltzmann methods)

- Problemas em grade não estruturada (p.ex. Elementos finitos)

- Método de Monte Carlo

- Lógica combinacional (p.ex. ataque de força bruta em criptografia)

- Travessia de grafos (p.ex. algoritmos de ordenação)

- Programação dinâmica

- Métodos branch and bound

- Modelos gráficos (p.ex. Hidden Markov model, rede bayesiana)

- Modelo HBJ de passagem de mensagens[62]

- Simulação de automato finito

Remove ads

Tolerância a falhas

Computação paralela pode ser aplicada a sistemas lockstep, executando operações em paralelo para redundância e detecção/correção de erros se resultados divergem. Útil contra single-event upsets transitórios.[63]

Histórico

Resumir

Perspectiva

As raízes do paralelismo MIMD remontam a Luigi Federico Menabrea e seu Sketch of the Analytic Engine Invented by Charles Babbage.[65][66][67]

Em 1957, a Compagnie des Machines Bull anunciou o primeiro design para paralelismo, o Gamma 60.[68] Ele usava modelo fork-join e um "Distribuidor de Programas" para comunicar-se com unidades independentes.[69][70]

Em abril de 1958, Stanley Gill (Ferranti) discutiu programação paralela e necessidade de branching e waiting.[71] Também em 1958, John Cocke e Daniel Slotnick (IBM) abordaram paralelismo em cálculos numéricos.[72] A Burroughs introduziu o D825 em 1962, um sistema de quatro processadores e 16 módulos de memória via crossbar.[73] Em 1967, Amdahl e Slotnick debateram o paralelo no AFIPS, cunhando a Lei de Amdahl.

Em 1969, a Honeywell lançou um sistema Multics SMP com até oito processadores.[74] O C.mmp (CMU, anos 1970) foi um dos primeiros multiprocessadores maiores. O Synapse N+1 (1984) foi o primeiro com cache snooping.[66]

Computadores SIMD datam dos anos 1970, visando amortizar latência de controle. Em 1964, Slotnick propôs o ILLIAC IV para LLNL, financiado pela Força Aérea dos EUA — o primeiro esforço SIMD massivo.[75][64] Quando rodou sua primeira aplicação real em 1976, já era ultrapassado por supercomputadores como o Cray-1.

Remove ads

Cérebro biológico como computador massivamente paralelo

Nos anos 1970, no MIT CSAIL, Marvin Minsky e Seymour Papert desenvolveram a teoria Society of Mind, que vê o cérebro como computação massivamente paralela. Em 1986, Minsky publicou The Society of Mind, afirmando que "a mente é formada por muitos pequenos agentes, cada um sem inteligência por si só".[76]

Modelos semelhantes foram propostos por:

- Thomas R. Blakeslee,[77]

- Michael Gazzaniga,[78][79]

- Robert E. Ornstein,[80]

- Ernest Hilgard,[81][82]

- Michio Kaku,[83]

- George Ivanovich Gurdjieff,[84]

- Modelo Neurocluster.[85]

Referências

- Gottlieb, Allan; Almasi, George S. (1989). Highly parallel computing (em inglês). Redwood City, Calif.: Benjamin/Cummings. ISBN 978-0-8053-0177-9

- S.V. Adve et al. (November 2008). "Parallel Computing Research at Illinois: The UPCRC Agenda" Arquivado em 2018-01-11 no Wayback Machine (PDF). Parallel@Illinois, University of Illinois at Urbana-Champaign. "The main techniques for these performance benefits—increased clock frequency and smarter but increasingly complex architectures—are now hitting the so-called power wall. The computer industry has accepted that future performance increases must largely come from increasing the number of processors (or cores) on a die, rather than making a single core go faster."

- Asanovic et al. Old [conventional wisdom]: Power is free, but transistors are expensive. New [conventional wisdom] is [that] power is expensive, but transistors are "free".

- Asanovic, Krste et al. (December 18, 2006). "The Landscape of Parallel Computing Research: A View from Berkeley" (PDF). University of California, Berkeley. Technical Report No. UCB/EECS-2006-183. "Old [conventional wisdom]: Increasing clock frequency is the primary method of improving processor performance. New [conventional wisdom]: Increasing parallelism is the primary method of improving processor performance… Even representatives from Intel, a company generally associated with the 'higher clock-speed is better' position, warned that traditional approaches to maximizing performance through maximizing clock speed have been pushed to their limits."

- Parallel and Concurrent Programming in Haskell. [S.l.]: O'Reilly Media. 2013. ISBN 9781449335922

- Hennessy, John L.; Patterson, David A.; Larus, James R. (1999). Computer organization and design: the hardware/software interface 2. , 3rd print. ed. San Francisco: Kaufmann. ISBN 978-1-55860-428-5

- Barney, Blaise. «Introduction to Parallel Computing» (em inglês). Lawrence Livermore National Laboratory. Consultado em 9 de novembro de 2007

- Thomas Rauber; Gudula Rünger (2013). Parallel Programming: for Multicore and Cluster Systems. [S.l.]: Springer Science & Business Media. p. 1. ISBN 9783642378010

- Hennessy, John L.; Patterson, David A. (2002). Computer architecture / a quantitative approach. 3rd ed. San Francisco, Calif.: International Thomson. p. 43. ISBN 978-1-55860-724-8

- Flynn, Laurie J. (8 de maio de 2004). «Intel Halts Development Of 2 New Microprocessors». New York Times. Consultado em 5 de junho de 2012

- Thomas Rauber; Gudula Rünger (2013). Parallel Programming: for Multicore and Cluster Systems. [S.l.]: Springer Science & Business Media. p. 2. ISBN 9783642378010

- Thomas Rauber; Gudula Rünger (2013). Parallel Programming: for Multicore and Cluster Systems. [S.l.]: Springer Science & Business Media. p. 3. ISBN 9783642378010

- Bakos, Jason D. (1 de janeiro de 2016), Bakos, Jason D., ed., «Chapter 2 - Multicore and data-level optimization: OpenMP and SIMD», ISBN 978-0-12-800342-8, Boston: Morgan Kaufmann, Embedded Systems, pp. 49–103, doi:10.1016/b978-0-12-800342-8.00002-x, consultado em 18 de novembro de 2024

- The Art of Multiprocessor Programming, Revised Reprint. [S.l.]: Morgan Kaufmann. 22 de maio de 2012. ISBN 9780123973375

- Vajda, András (10 de junho de 2011). Programming Many-Core Chips. [S.l.]: Springer. ISBN 9781441997395

- Amdahl, Gene M. (18 de abril de 1967). «Validity of the single processor approach to achieving large scale computing capabilities». Proceedings of the April 18-20, 1967, spring joint computer conference on - AFIPS '67 (Spring). New York, NY, USA: Association for Computing Machinery. pp. 483–485. ISBN 978-1-4503-7895-6. doi:10.1145/1465482.1465560

- Computer Architecture: A Quantitative Approach. [S.l.]: Morgan Kaufmann. 2003. ISBN 978-8178672663

- Parallel Computer Architecture A Hardware/Software Approach. [S.l.]: Elsevier Science. 1999. ISBN 9781558603431

- McCool, Michael; Reinders, James; Robison, Arch (2013). Structured Parallel Programming: Patterns for Efficient Computation. [S.l.]: Elsevier. 61 páginas. ISBN 978-0-12-415993-8

- Gunther, Neil (2007). Guerrilla Capacity Planning: A Tactical Approach to Planning for Highly Scalable Applications and Services. [S.l.: s.n.] ISBN 978-3540261384

- Bernstein, Arthur J. (1 de outubro de 1966). «Analysis of Programs for Parallel Processing». IEEE Transactions on Electronic Computers. EC-15 (5): 757–763. doi:10.1109/PGEC.1966.264565

- Roosta, Seyed H. (2000). Parallel processing and parallel algorithms : theory and computation. New York, NY [u.a.]: Springer. p. 114. ISBN 978-0-387-98716-3

- «Processes and Threads». Microsoft Developer Network. Microsoft Corp. 2018. Consultado em 10 de maio de 2018

- Krauss, Kirk J (2018). «Thread Safety for Performance». Develop for Performance. Consultado em 10 de maio de 2018. Cópia arquivada em 13 de maio de 2018

- Tanenbaum, Andrew S. (1 de fevereiro de 2002). Introduction to Operating System Deadlocks. Informit. [S.l.]: Pearson Education, Informit. Consultado em 10 de maio de 2018

- Cecil, David (3 de novembro de 2015). «Synchronization internals – the semaphore». Embedded. AspenCore. Consultado em 10 de maio de 2018

- Preshing, Jeff (8 de junho de 2012). «An Introduction to Lock-Free Programming». Preshing on Programming. Consultado em 10 de maio de 2018

- «What's the opposite of "embarrassingly parallel"?». StackOverflow. Consultado em 10 de maio de 2018

- Schwartz, David (15 de agosto de 2011). «What is thread contention?». StackOverflow. Consultado em 10 de maio de 2018

- Kukanov, Alexey (4 de março de 2008). «Why a simple test can get parallel slowdown». Consultado em 15 de fevereiro de 2015

- Krauss, Kirk J (2018). «Threading for Performance». Develop for Performance. Consultado em 10 de maio de 2018. Cópia arquivada em 13 de maio de 2018

- Patterson and Hennessy, p. 748.

- Silberschatz, Abraham; Galvin, Peter B.; Gagne, Greg (29 de julho de 2008). Operating System Concepts. [S.l.]: Wiley. ISBN 978-0470128725

- Computer Organization and Design MIPS Edition: The Hardware/Software Interface. [S.l.]: Morgan Kaufmann. 2013. ISBN 978-0124077263

- Parallel Programming: Techniques and Applications Using Networked Workstations and Parallel Computers. [S.l.]: Pearson. 2005. ISBN 978-0131405639

- Culler et al. p. 15.

- Patt, Yale (April 2004). "The Microprocessor Ten Years From Now: What Are The Challenges, How Do We Meet Them?" (wmv). Distinguished Lecturer, CMU. Retrieved on November 7, 2007.

- Culler et al. p. 124.

- Culler et al. p. 125.

- Samuel Larsen; Saman Amarasinghe. «Exploiting Superword Level Parallelism with Multimedia Instruction Sets» (PDF)

- Patterson and Hennessy, p. 713.

- Hennessy and Patterson, p. 549.

- Patterson and Hennessy, p. 714.

- Lynch (1996), p. xix–1.

- Peleg (2000), p. 1.

- Webopedia

- PC Magazine

- «List Statistics». Top500

- Hennessy and Patterson, p. 537.

- PC Magazine

- Kirkpatrick, Scott (2003). Science. 299 (5607): 668–669. doi:10.1126/science.1081623

- Valueva, Maria (2019). Electronics. 8 (6). 694 páginas. doi:10.3390/electronics8060694

- Gupta, Ankit (maio de 2020). https://ieeexplore.ieee.org/document/9121004. [S.l.]: IEEE. pp. 496–498. doi:10.1109/ICICCS48265.2020.9121004 Em falta ou vazio

|título=(ajuda) - D'Amour, Michael R. (2007). "Standard Reconfigurable Computing". University of Delaware.

- Boggan & Pressel (2007). ARL-SR-154, U.S. Army Research Lab.

- Kahng, Andrew B. (2004). Future Fab. "DFM Mask Cost".

- Patterson and Hennessy, p. 751.

- Sidney Fernbach Award for MPI inventor Bill Gropp

- Shen, John Paul; Lipasti, Mikko H. (2004). Modern processor design: fundamentals of superscalar processors. [S.l.]: McGraw-Hill. p. 561

- Padua, D. (2011). Encyclopedia of Parallel Computing, Vol. 4, p. 265.

- Adve et al. (2006). Parallel Computing Research at Illinois.

- Helman, David R.; Bader, David A.; JaJa, Joseph (1998). «A Randomized Parallel Sorting Algorithm with an Experimental Study». Journal of Parallel and Distributed Computing. 52: 1–23. doi:10.1006/jpdc.1998.1462

- Dobel, B., Hartig, H., & Engel, M. (2012). "Operating system support for redundant multithreading". Proceedings of the Tenth ACM International Conference on Embedded Software, 83–92. doi=10.1145/2380356.2380375

- Patterson and Hennessy, pp. 749–50: "Although successful in pushing several technologies useful in later projects, the ILLIAC IV failed as a computer...Costs escalated from $8 million in 1966 to $31 million by 1972 for only a quarter-built machine."

- Menabrea, L. F. (1842). Sketch of the Analytic Engine Invented by Charles Babbage. Bibliothèque Universelle de Genève.

- Patterson and Hennessy, p. 753.

- Hockney & Jesshope (1988). Parallel Computers 2, p. 8

- Bataille, M. (1 de abril de 1972). «Something old: the Gamma 60 the computer that was ahead of its time». ACM SIGARCH Computer Architecture News. 1 (2): 10–15. ISSN 0163-5964. doi:10.1145/641276.641278

- Mark Smotherman. Architecture Sketch of Bull Gamma 60.

- Tumlin & Smotherman (2023). An Evaluation of the Design of the Gamma 60.

- "Parallel Programming", S. Gill, The Computer Journal, Vol. 1 #1, April 1958.

- Gregory V. Wilson (1994). «The History of the Development of Parallel Computing»

- Anthes, Gry (2001). The Power of Parallelism. Computerworld.

- Gregory V. Wilson. «Honeywell Multics SMP»

- Gregory V. Wilson (1994). «The History of the Development of Parallel Computing»

- Minsky, Marvin (1986). The Society of Mind. New York: Simon & Schuster. pp. 17. ISBN 978-0-671-60740-1

- Blakeslee, Thomas (1996). Beyond the Conscious Mind. Unlocking the Secrets of the Self. [S.l.]: Springer. ISBN 9780306452628

- Gazzaniga, Michael; LeDoux, Joseph (1978). The Integrated Mind. [S.l.: s.n.] pp. 132–161

- Gazzaniga, Michael (1985). The Social Brain. Discovering the Networks of the Mind. [S.l.]: Basic Books. ISBN 9780465078509

- Ornstein, Robert (1992). Evolution of Consciousness: The Origins of the Way We Think. [S.l.: s.n.]

- Hilgard, Ernest (1977). Divided consciousness: multiple controls in human thought and action. [S.l.]: Wiley. ISBN 978-0-471-39602-4

- Hilgard, Ernest (1986). Divided consciousness: multiple controls in human thought and action (expanded edition). [S.l.]: Wiley. ISBN 978-0-471-80572-4

- Kaku, Michio (2014). The Future of the Mind. [S.l.: s.n.]

- Ouspenskii, Pyotr (1992). In Search of the Miraculous. Fragments of an Unknown Teaching. [S.l.: s.n.]

- «Official Neurocluster Brain Model site». Consultado em 22 de julho de 2017

Remove ads

Ligações externas

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads