热门问题

时间线

聊天

视角

签核

来自维基百科,自由的百科全书

Remove ads

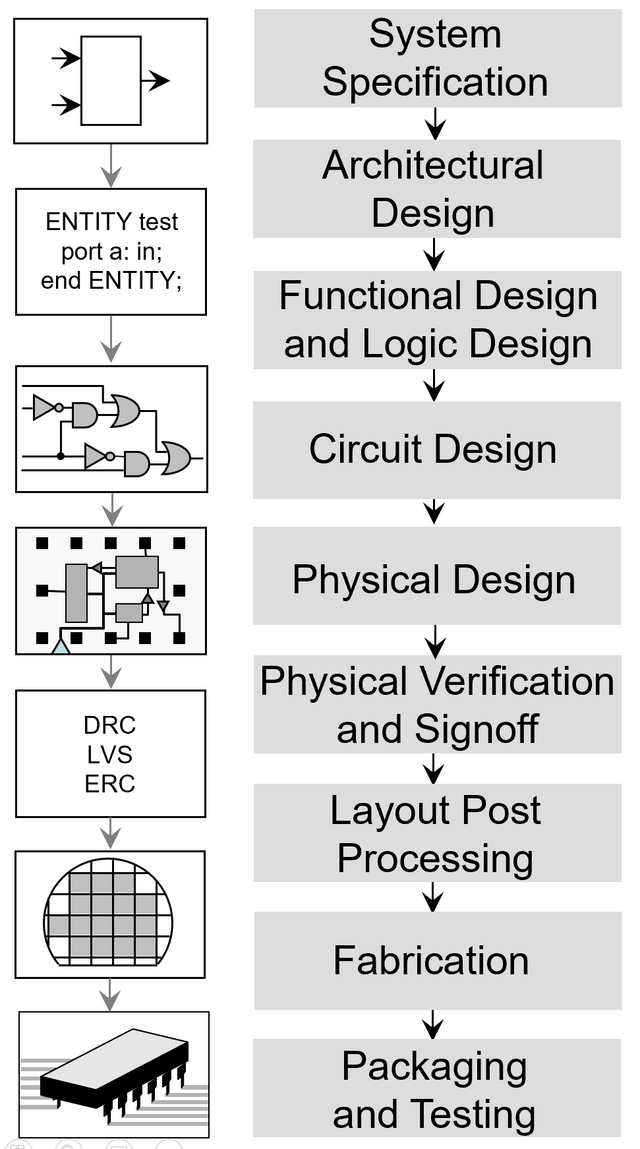

签核(signoff,sign-off)检查在集成电路设计自动化中,是指设计在可以流片之前必须通过的一系列验证步骤的统称。 这意味着一个迭代过程,涉及使用一种或多种检查类型在各处进行增量修复,然后重新测试设计。 签核分为两类:前道签核和后道签核。 后道签核之后,芯片进入制造。在列出规范中的所有特性后,验证工程师会为这些特性编写覆盖率以识别缺陷,并将RTL设计返还给设计师。 缺陷可能包括与规范相比的缺失特性、设计错误(如笔误和功能性错误)等。 当覆盖率达到最大百分比时,验证团队将对其签核。 通过采用像UVM、OVM或VMM这样的验证方法学,验证团队可以开发可复用的验证环境。 目前UVM比其他方法更为流行。

历史

在二十世纪六十年代末,像英特尔这样的半导体公司工程师使用Rubylith来制作半导体光刻掩模。 工程师手工绘制的半导体器件电路图由熟练的原理图绘制员手工转移到D尺寸的犊皮纸上,以在光掩模上制作器件的物理版图。[1]:6

这些犊皮纸随后由原工程师手工检查并予以“签核”;对原理图的所有修改也会被记录、检查并再次“签核”。[1]:6

检查类型

随着超大规模集成电路设计接近22纳米制程及更小工艺节点,签核检查变得更加复杂,原因是先前被忽略或粗略近似的二阶效应影响增大。 签核检查分为若干类别。

- 设计规则检查(DRC)有时称为几何验证。 它用于验证在当前光刻限制下设计是否可以可靠制造。 在先进工艺节点,DFM规则从可选(以提高良率)升级为必需。

- 形式验证将版图后网表(包括任何由版图驱动的优化)的逻辑功能与版图前、综合后的网表进行验证。

- 电压降分析 — 也称为IR-drop分析。 此检查验证电源网格是否足够强,以保证代表二进制高电平的电压不会因数百万晶体管的共同切换而跌落到低于电路可靠工作所需的裕度。

- 信号完整性分析——分析由串扰等问题造成的噪声,并检查其对电路功能的影响,确保电容性毛刺不足以越过数据路径上门的阈值电压。

- 静态时序分析(STA)正逐步被统计静态时序分析(SSTA)取代。 STA用于验证设计中所有逻辑数据路径在目标时钟频率下能否工作,特别是在芯片工艺变动影响下。 STA用作替代SPICE,因为SPICE模拟的运行时间使其对现代设计的全芯片分析不可行。

- 电迁移寿命检查——保证在目标时钟频率下操作时,电路不会因电迁移而失效,从而满足最小寿命要求。

- 功能静态签核检查——使用搜索和分析技术检查所有可能的测试用例下的设计失败;功能静态签核域包括时钟域交叉、复位域交叉和 X 传播。

- 功能静态签核检查——使用搜索和分析技术在所有可能测试用例下检查设计失效;功能性静态签核领域包括时钟域跨越、复位域跨越和X传播。

Remove ads

工具

一小部分工具被归类为“金牌”或签核级工具。 在不带供应商偏见的情况下将工具归类为签核级,通常依靠试错法,因为只有在设计制造出来后才能确定工具的准确性。 因此,一个常用(并常被工具厂商宣称)的衡量指标是该工具促成的成功流片次数。 有人认为该指标不足、定义不清且对某些工具无关,尤其是那些仅在完整流程中起部分作用的工具。[2]

虽然厂商常夸大其工具套件在端到端(通常是从RTL到GDS对于ASIC,以及从RTL到时序收敛对于FPGA)执行上的便利, 大多数半导体设计公司仍然使用来自不同厂商的组合工具(常称为“最佳”工具),以最小化片上和片后相关性误差。[3] 由于独立工具评估成本高昂(主要厂商如新思科技与Cadence的设计工具单一许可可能花费数万到数十万美元)且风险较大(如果在生产设计上评估失败,会导致上市时程延迟),因此只有最大的设计公司(如英特尔、IBM、飞思卡尔和德州仪器)才有条件进行。 作为一种增值服务,若干半导体代工厂现在提供预评估的参考/推荐方法学(有时称为“RM”流程),其中包含推荐工具、版本和用于在工具间移动数据并自动化整个流程的脚本清单。[4][5]

下列供应商和工具为代表性列举,非详尽:

- DRC/LVS - Mentor HyperLynx DRC Free/Gold 、 Mentor Calibre 、 Magma Quartz 、 Synopsys Hercules 、 Cadence Assura

- 电压降分析 - Cadence Voltus 、 Apache Redhawk 、 Magma Quartz Rail

- 信号完整性分析 - Cadence CeltIC (串扰噪声)、 Cadence Tempus Timing Signoff Solution 、 Synopsys PrimeTime SI (串扰延迟/噪声)、 Extreme-DA GoldTime SI (串扰延迟/噪声)

- 静态时序分析 - Synopsys PrimeTime 、 Magma Quartz SSTA 、 Cadence ETS 、 Cadence Tempus Timing Signoff Solution 、 Extreme-DA GoldTime

参考

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads