热门问题

时间线

聊天

视角

PCI Express

计算机扩展总线标准 来自维基百科,自由的百科全书

Remove ads

外围组件快速互连[1](Peripheral Component Interconnect Express),简称PCI-E,官方简称PCIe,是计算机总线的一个重要分支,它沿用既有的PCI编程概念及信号标准,并且构建了更加高速的串行通信系统标准。目前这一标准由PCI-SIG组织制定和维护。PCIe仅应用于内部互连。由于PCIe是基于既有的PCI系统,所以只需修改物理层而无须修改软件就可将现有PCI系统转换为PCIe。

PCIe拥有更快的速率,所以几乎取代了以往所有的内部总线(包括AGP和PCI)。现在英特尔和AMD已采用单芯片组技术,取代原有的南桥和北桥方案。

除此之外,PCIe设备能够支援热拔插特性,目前支援的三种电压分别为+3.3V、3.3Vaux以及+12V。

考虑到现在显卡功耗的日益增加,PCIe而后在规范中改善了直接从插槽中取电的功率限制,×16的最大提供功率一度达到了75W[2],相对于AGP 8X接口有了很大的提升。

PCIe保证了相容性,支援PCI的作业系统无需进行任何更改即可支援PCIe总线。这也给用户的升级带来方便。由此可见,PCIe最大的意义在于它的通用性,不仅可以让它用于南桥和其他设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形处理器,这样,整个I/O系统重新统一起来,将更进一步简化计算机系统,增加计算机的可移植性和模块化。

Remove ads

历史

在2001年的春季英特尔开发者论坛(IDF)上Intel公布取代PCI总线的第三代I/O技术,被称为“3GIO”。该总线的规范由Intel支持的AWG(Arapahoe Work Group)负责制定。2002年4月17日,AWG正式宣布3GIO 1.0规范草稿制定完毕,移交PCI特殊兴趣组织(PCI-SIG)进行审核,2002年7月23日经过审核后正式公布,改名为“PCI Express”,并根据开发蓝图在2006年正式推出Spec 2.0(2.0规范)。[3][4]2019年5月28日,PCI-SIG官方发布了PCIe 5.0的1.0版基础规范,规范主要定义了PCIe5.0的架构(architecture)、互联属性规范(interconnect attributes)、网络结构管理(fabric management)以及编程接口(programming interface)等内容[5]。

以PCIe 2.0为例,每秒5GT(Gigatransfer)原始数据传输率,编码方式为8b/10b(每10个位元只有8个有效数据),即有效频宽为4Gb/s = 500MByte/s。

Remove ads

PCI Express与其他传输规格比较

PCIe的规范主要是为了提升电脑内部所有汇流排的速度,因此频宽有多种不同规格标准,其中PCIe ×16是特别为显示卡所设计。AGP的资料传输效率最高为2.1GB/s,不过对上PCIe ×16的8GB/s,很明显的就分出胜负,但8GB/s是指资料传输的理想值,并不是使用PCIe介面的显示卡,就能够有突飞猛进的效能表现,实际的测试数据并不会有这么大的差异存在。 [10][11]

计算公式:PCI-E串行总线带宽(MB/s) = 串行总线时钟频率(MHz)* 串行总线位宽(bit/8 = B)* 串行总线管线* 编码方式* 每时钟传输几组数据(cycle),例:双工PCI-E 1.0 X1,其带宽 = 2500*1/8*1*8/10*1*2=500 MB/s。

PCI Express 1.0总线频率2500 MHz,这是在100 MHz的基准频率通过锁相环振荡器(Phase Lock Loop,PLL)达到的。PCI-E 2.0总线频率从2.5GHz提高到5GHz,3.0则提高到8GHz,编码方式变成128/130。

Remove ads

PCI Express的硬件协议

PCIe的连接是建立在一个单向的序列的(1-bit)点对点连接基础之上,这称之为通道(lane)。这一点上PCIe连接与早期PCI连接形成鲜明对比,PCI连接基于总线控制,所有设备共享双向32位并行总线。PCIe是一个多层协议,由事务层,数据交换层和物理层构成。物理层又可进一步分为逻辑子层和电气子层。逻辑子层又可分为物理代码子层(PCS)和介质接入控制子层(MAC)。这些术语借用自 IEEE 802 网络协议模型。PCIe通过ASPM协定进行电源管理。

于使用电力方面,每组流水线使用两个单向的低电压差分信号(LVDS)合计达到2.5 Gbit/s。传送及接收不同数据会使用不同的传输通道,每一通道可运作四项资料。两个PCIe设备之间的连接成为“链接”,这形成1组或更多的传输通道。各个设备最少支援1传输通道(x1)的链接。也可以有2,4,8,16,32个通道的链接。这可以更好的提供双向兼容性(x2模式将用于内部接口而非插槽模式)。PCIe卡能使用在至少与之传输通道相当的插槽上(例如x1接口的卡也能工作在x4或x16的插槽上)。一个支援较多传输通道的插槽可以建立较少的传输通道(例如8个通道的插槽能支援1个通道)。PCIe设备之间的链接将使用两设备中较少通道数的作为标准。一个支援较多通道的设备不能在支援较少通道的插槽上正常工作,例如x4接口的卡不能在x1的插槽上正常工作(插不入),但它能在x4的插槽上只建立1个传输通道(x1)。PCIe卡能在同一数据传输通道内传输包括中断在内的全部控制信息。这也方便与PCI的兼容。多传输通道上的数据传输采取交叉存取,这意味着连续字节交叉存取在不同的通道上。这一特性被称之为“数据条纹”,需要非常复杂的硬件支援连续数据的同步存取,也对链接的数据吞吐量要求极高。由于数据填充的需求,数据交叉存取不需要缩小数据包。与其它高速数传输协议一样,时钟信息必须嵌入信号中。在物理层上,PCIe采用常见的8B/10B代码方式来确保连续的1和0字符串长度符合标准,这样保证接收端不会误读。编码方案用10位编码比特代替8个未编码比特来传输数据,占用20%的总带宽。到了PCIe 3.0,采用128B/130B代码方式,仅占用1.538%的总带宽。有些协议(如SONET)使用另外的编码结构如“不规则”在数据流中嵌入时钟信息。PCIe的特性也定义一种“不规则化”的运算方法,但这种方法与SONET完全不同,它的方法主要用来避免数据传输过程中的数据重复而出现数据散射。第一代PCIe采用2.5GT/s单信号传输率,PCI-SIG计划在未来版本中增强到5~10GT/s。

Remove ads

数据链路层采用按序的交换层信息包(Transaction Layer Packets,TLPs),是由交换层生成,按32位循环冗余校验码(CRC,本文中用LCRC)进行数据保护,采用著名的协议(Ack and Nak signaling)的信息包。TLPs能通过LCRC校验和连续性校验的称为Ack(命令正确应答);没有通过校验的称为Nak(没有应答)。没有应答的TLPs或者等待逾时的TLPs会被重新传输。这些内容存储在数据链路层的缓存内。这样可以确保TLPs的传输不受电子噪音干扰。PCIe对于ACK有所规范,在收到TLP封包之后,在一定时间内必须回应ACK,也就是ACK延迟(ACK Latency)的等待时间。因应ACK/NAK流程的需要,必须实作出重新播送缓冲器(Replay Buffer)。

TLPs加上Sequence number以及16 位元 CRC 后,被包裹成为数据链路层信息包(Data Link Layer Packet,DLLP),除了资料传递外,交握信号ACK和NAK信号亦被包裹在信息包中传送,除此之外也用来传送两个互连设备的交换层之间的流控制信息和实现电源管理功能。

Remove ads

PCI Express采用分离交换(数据提交和应答在时间上分离),可保证传输通道在目标端设备等待发送回应信息传送其它数据信息。

PCI Express采用可信性流控制。这一模式下,一个设备广播它可接收缓存的初始可信信号量。链接另一方的设备会在发送数据时统计每一发送的TLP所占用的可信信号量,直至达到接收端初始可信信号最高值。接收端在处理完毕缓存中的TLP后,它会回送发送端一个比初始值更大的可信信号量。可信信号统计是定制的标准计数器,相比于其他方法,如基于握手的传输协议,这一模式的优势在于可信信号的回传反应时间不会影响系统性能,因为如果双方设备的缓存足够大,是不会出现达到可信信号最高值的情况,这样发送数据不会停顿。

第一代PCIe标称可支援每传输通道单向每秒250 MB的数据传输率。这一数字是根据物理信号率2500 Mbit/s除以编码率(10位/每字节)计算而得。这意味着一个16通道(x16)的PCIe卡理论上可以达到单向250*16=4000 MB/s(3.7 GB/s)。实际的传输率要根据数据有效载荷率,即依赖于数据的本身特性,这是由更高层(软件)应用程序和中间协议层决定。

PCI Express与其它高速序列连接系统相似,它依赖于传输的强健性(CRC校验和ACK)。长时间连续的单向数据传输(如高速存储设备)可以达到>95%的PCIe通道数据传输利用率。这样的传输受益于增加的传输通道(x2, x4 等)。但大多数应用程序如USB或乙太网路控制器会把传输内容拆成小的数据包,同时还会强制加上确认信号。这类数据传输由于增加数据包的解析和强制中断,降低传输通道的效率。作为一个在同一个印刷电路板(PCB)设备间的通信协议,它不需要达到其他远距离通信协议要求的高数据传输错误容忍度,而且,这种效率的降低并非只出现在PCIe上。

Remove ads

下表列出在边缘连接器上的PCI Express卡两侧的导线。在印刷电路板(PCB)的焊接侧为A侧,并且组件侧的B侧。[12]PRSNT1# 和PRSNT2# 引脚必须比其馀稍短,以确保热插入卡完全插入。该WAKE# 引脚采用全电压唤醒计算机,但必须拉高从备用电源,以表明该卡是能够唤醒。[13]

Remove ads

制式标准

- 半高卡

- Mini PCIe:用以代替Mini PCI卡(支援x1 PCIe、USB 2.0和SMBus总线接口)。

- ExpressCard:类似PC卡接口标准(支援x1 PCIe、USB 2.0/3.0、热插拔)。

- PCI Express ExpressModule:支援热插拔的接口标准,用于伺服器和工作站上。

- XMC:类似CMC/PMC接口标准(支援x4 PCIe或串行RapidI/O)。

- AdvancedTCA:用以代替Compact PCI卡,支援串行背板拓扑结构基础。

- AMC:AdvancedTCA规范的补充,支援处理器和I/O模块在ATCA板上(x1、x2、x4或x8 PCIe)。

- PCI Express外置接线[14]。

- Mobile PCI Express Module(MXM)英伟达所发明的图形模块规范。

- Advanced eXpress I/O Module(AXIOM)图形模块,由ATI认可。

- Thunderbolt

- M.2

- U.2

Remove ads

竞争协议

基于高速序列构架产生了很多传输标准,包括HyperTransport、InfiniBand、RapidIO和StarFabric等等。这些标准均有业界的不同企业支援,背后也都有大量的资金投入标准的研究开发,所以每一标准都声称自己与众不同,独占优势。主要的差异在于可扩展性、灵活性与反应时间、单位成本的取舍平衡各不相同。其中的一个例子是在传输包上增加一个复杂的头信息以支援复杂路由传输(PCI Express不支援这种方式)。这样的信息增加降低了接口的有效带宽也使传输更复杂,但是相应创造了新的软件支援此功能。这种架构下需要软件追踪网络拓扑结构的变化以实现系统支援热插拔。InfiniBand和StarFabric标准即能实现这一功能。另一个例子是缩小信息包以减少反应时间。较小的信息包意味着包头占用了包的更大百分比,这样又降低了有效带宽。能实现此功能的标准是RapidIO和HyperTransport。PCI Express取中庸之道,定位于设计成一种系统互连接口而非一种设备接口或路由网络协议。另外为了针对软件透明,它的设计目标限制了它作为协议,也在某种程度上增加了它的反应时间。

应用与前景

在2005年,PCIe已近乎成为新的个人电脑主机板标准。关于此有不少评论,但最基本的原因是它对于软件开发者完全透明——为PCI所设计的操作系统可以不做任何代码修改来启动PCIe设备。其二,它能增强系统性能,还有强有力的品牌认知。各类网卡、声卡、显卡,以及当下的NVMe固态硬碟都使用了PCIe标准。下面为主流的使用PCIe 的外设产品。

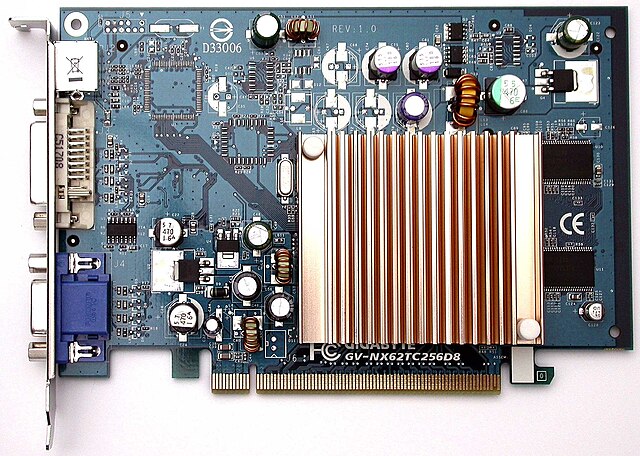

大部分新型的AMD或NVIDIA显卡都使用PCIe标准。NVIDIA在它新开发的SLI上采用PCIe的高速数据传输,这使得两块相同芯片组显卡可同时工作于一台电脑之上。AMD公司也基于PCIe开发一种两个GPU一同运作的技术,称为CrossFire。

当下主流的固态硬盘介面有M.2、U.2、PCIe、SATA、SATA Express、SAS等。M.2和U.2可选PCIe介面[15]。NVMe协议是目前最高效的PCIe SSD协议标准。

参考文献

参见

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads