热门问题

时间线

聊天

视角

平面工藝

来自维基百科,自由的百科全书

Remove ads

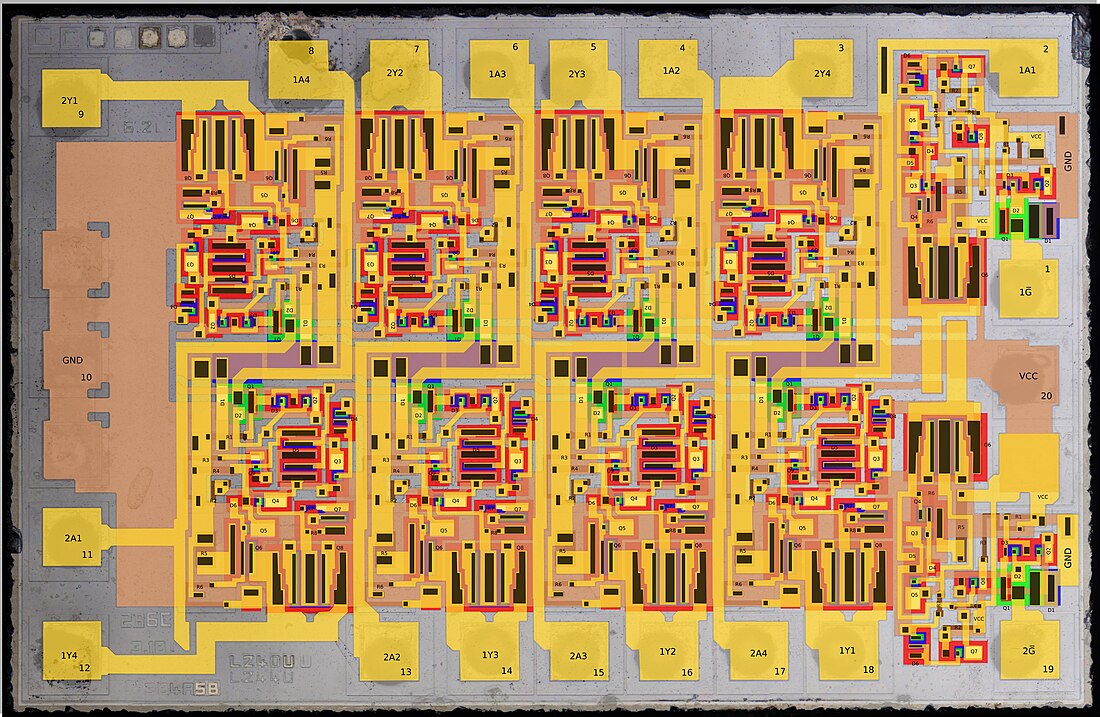

平面工藝是半導體產業中用於構建單個電晶體的各個組件,並將這些電晶體連接在一起的製造工藝。它是製造矽集成電路晶片的主要工藝,也是製造半導體器件時生成結的最常用方法。[1]該工藝利用表面鈍化和熱氧化方法。

概述

平面工藝的關鍵概念是將電路視為其二維投影(平面),從而可以使用諸如膠片底片等光刻沖洗概念來遮蔽曝光化學劑的投影。這允許在襯底(矽)上通過一系列曝光來形成二氧化矽(絕緣體)或摻雜區域(導體)。結合金屬化技術,以及p–n結隔離和表面鈍化的概念,可以在單個單晶矽晶棒切片(晶圓)上創建電路。

該工藝涉及二氧化矽(SiO2)氧化、SiO2蝕刻和熱擴散等基本步驟。最後階段是在整個晶圓上形成一層SiO2,蝕刻出與電晶體的接觸通孔,並在氧化物層上沉積金屬覆蓋層,從而無需手工布線即可將電晶體連接在一起。

歷史

1955年,在貝爾實驗室,卡爾·弗羅施和Lincoln Derick偶然在矽晶圓上生長出一層二氧化矽,並觀察到其具有表面鈍化特性。[2][3]1957年,Frosch和Derick製造了首批二氧化矽場效應電晶體,這是第一種源極和漏極在表面相鄰的電晶體,證明了二氧化矽表面鈍化可以保護並絕緣矽晶圓。[4]

卡爾·弗羅施的技術重要性在貝爾實驗室迅速得到認可。他們的成果以BTL備忘錄的形式在實驗室內部流傳,並於1957年正式發表。在肖克利半導體實驗室,威廉·肖克利於1956年12月向其高級員工(包括金·赫爾尼)分發了該論文的預印本。[5][6][7][8]後來,赫爾尼在一次會議上聽取了阿塔拉關於基於貝爾實驗室成果的鈍化論文。[8]利用二氧化矽對矽表面的鈍化效果,赫爾尼提出用二氧化矽層保護電晶體。[8]

赫爾尼在快捷半導體工作期間,於1959年首次為平面工藝申請了專利。[9][10]貝爾實驗室的K. E. Daburlos和H. J. Patterson同時進行了類似研究,也在同一時期發展出與赫爾尼相似的工藝。[8]結合金屬化(用於連接集成電路)和來自Kurt Lehovec的p–n結隔離概念,快捷半導體的研究人員得以在單個單晶矽晶錠(晶圓)上製造電路。

1959年,羅伯特·諾伊斯在赫爾尼工作基礎上提出了集成電路的概念,在赫爾尼結構頂部增加了一層金屬,用於連接同一矽片上的不同組件,如電晶體、電容器或電阻器。平面工藝為實現集成電路提供了強大手段,優於早期集成電路的構想。[11][12][13]

早期平面工藝版本使用來自汞蒸氣燈的近紫外光進行光刻曝光。至2011年,小尺寸特徵通常採用193 nm「深紫外」光刻技術。[14]至2022年,艾司摩爾的NXE平台在極紫外光刻(13.5 nm)中使用錫基等離子體光源。

相關

參考

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads