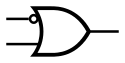

蕴涵门[1](英语:Implies gate,简称IMPLY gate)[2]是数字逻辑电路中的一种逻辑门,主要用来完成布尔代数中实质条件、实质蕴涵或蕴涵算子。

| 基本逻辑闸 | |

| 缓冲 | 非 |

| 与 | 与非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蕴含 | 蕴含非 |

| 输入 A B |

输出 A → B | |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

另外蕴涵门也可以由忆阻器组成,且只需要由两个忆阻器即可组成[3][4],由于布尔代数的特性可使其他布尔函数化成由逻辑蕴含表示[5],因此利用蕴涵门与忆阻器来设计晶体管可以大幅缩小体积[6]。

性质

| 输入 A B |

输出 A → B | |

| X | 1 | 1 |

| 0 | 0 | 1 |

| 1 | 0 | 0 |

- 如果B为逻辑真, 无论A为任何值都会输出逻辑真的信号。

- 其中,X代表输入的是无论何值皆可。

- 如果B为逻辑假, 并且A为逻辑假, 才会输出逻辑真的信号。

- 其余情况则输出逻辑假的信号。

- 蕴涵门可以用来判断两输入的或是否为第二输入。

概述

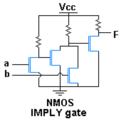

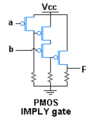

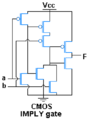

电路实现

复合逻辑门

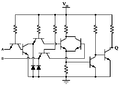

大部分的逻辑门都可以用蕴涵门组合而成,例如与非门可以用两个蕴涵门组合而成[9]:

其他逻辑门

蕴含非闸,简称NIMPLY gate是数字逻辑电路中实现非蕴涵的一种逻辑门。

这种运作方式的器件已在生物学的逻辑信号中有相关研究。[10]

参见

查看维基词典中的词条“implication gate”。

参考文献

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.

, ...

, ...

, ...

, ...