锁相环

维基百科,自由的 encyclopedia

锁相环(PLL: Phase-locked loops)是利用回授(Feedback)控制原理实现的频率及相位的控制系统,其作用是将电路输出的信号与其外部的参考信号保持同步,当参考信号的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的回授系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

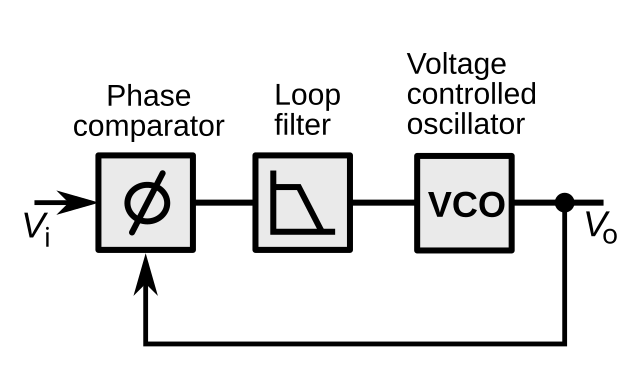

锁相环有许多种,最简单的锁相环会包括变频振荡器(英语:variable frequency oscillator)以及鉴相器,形成回授回路。振荡器产生讯号,鉴相器比较输出讯号和输入周期讯号之间的相位,调整振荡器输出,设法和输入周期讯号同步。

若让输出讯号和输入讯号之间的相位一致,则两者的频率也会一致。因此,锁相环除了让相位一致之外,也可以追踪输入讯号的频率,或是产生频率是输入讯号整数倍的信号。此特性可以用在电脑时脉的同步、解调变(英语:demodulation)及频率合成(英语:frequency synthesis)。

锁相环常用在无线电、电信、电子计算机及其他电子设备中。锁相环也可以用来解调变讯号、从高噪声的通讯频道中恢复原始信号、产生频率为输入信号频率整数倍的频率(频率合成)、或在数字电路(例如微处理器)中产生准确的时钟脉冲。因为单一的集成电路即可提供完整的锁相环机能,此技术已普遍使用在现在的电子设备中,输出频率从1Hz以下,到数GHz。