Timeline

Chat

Prospettiva

Porta OR

tipo di porta logica digitale Da Wikipedia, l'enciclopedia libera

Remove ads

La porta OR (dalla congiunzione inglese or, "o") è una porta logica digitale che implementa la disgiunzione logica: essa si comporta come la tabella di verità a destra. Quando entrambe le sue entrate (input) sono su 0 (zero) o su BASSA, la sua uscita (output) è su 0 o su BASSA, mentre quando una sola delle sue entrate è su 1 (uno) o su ALTA, la sua uscita sarà su 1 o su ALTA. In altre parole, la funzione OR trova effettivamente il massimo tra due cifre binarie, proprio come la funzione complementare AND (equivalente alla congiunzione "e") trova il minimo tra due cifre binarie.

| INPUT A B | OUTPUT A + B | |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Remove ads

Simboli

Si usano tre simboli per le porte OR: il simbolo statunitense (ANSI o "militare") e il simbolo IEC ("europeo" o "rettangolare"), oltre al simbolo deprecato DIN.[1][2] Per una panoramica generale sui simboli delle porte logiche vedi la voce Porta logica.

|

|

|

| Simbolo MIL/ANSI | Simbolo IEC | simbolo DIN |

Remove ads

Descrizione hardware e disposizione dei contatti

Le porte OR sono porte logiche basilari e come tali sono disponibili nelle famiglie logiche di circuiti integrati (CI) TTL e CMOS. Il CI standard CMOS serie 4000 è il 4071, che comprende quattro porte OR indipendenti a 2 entrate. La versione TTL tradizionale è la 7432. Ci sono molti derivati della porta OR originale 7432. Tutte hanno la stessa disposizione dei contatti o piedini ("piedinatura"), ma diversa architettura interna, il che consente loro di operare in diversi intervalli di tensione e/o a velocità superiori. In aggiunta alla porta OR standard a 2 entrate, sono disponibili anche porte a 3 e a 4 entrate. Nella serie CMOS, queste sono:

- 4075: tripla porta OR a 3 entrate

- 4072: porta OR duale a 4 entrate.

Le variazioni TTL comprendono:

- 74LS32: porta OR quadrupla a 2 entrate (versione Schottky a bassa potenza)

- 74HC32: porta OR quadrupla a 2 entrate (versione CMOS ad alta velocità) - ha minore consumo di corrente/più ampio intervallo di tensione

- 74LVC32: versione CMOS della stessa porta a bassa tensione.

Remove ads

Linguaggio di descrizione dell'hardware

modulo(a,b,c); entrata a,b; uscita c; or (c,a,b); fine;

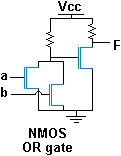

Implementazioni

|  |

Alternative

Se non sono disponibili porte OR specifiche, se ne può ricavare una dalle porte NAND o NOR nella configurazione mostrata nell'immagine a destra di questo testo. Qualsiasi porta logica può essere ricavata da una combinazione di porte NAND o NOR.

OR cablato

Con uscite logiche attive-basse dotate di collettore aperto, usate per i segnali di controllo in molti circuiti, una funzione OR può essere prodotta cablando insieme varie uscite. Questa disposizione è chiamata OR cablato. Questa implementazione di una funzione OR si trova tipicamente nei circuiti integrati dei processi con soli transistor di tipo N o P.

Remove ads

Note

Voci correlate

Altri progetti

Collegamenti esterni

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads