Timeline

Chat

Prospettiva

Processo planare

Da Wikipedia, l'enciclopedia libera

Remove ads

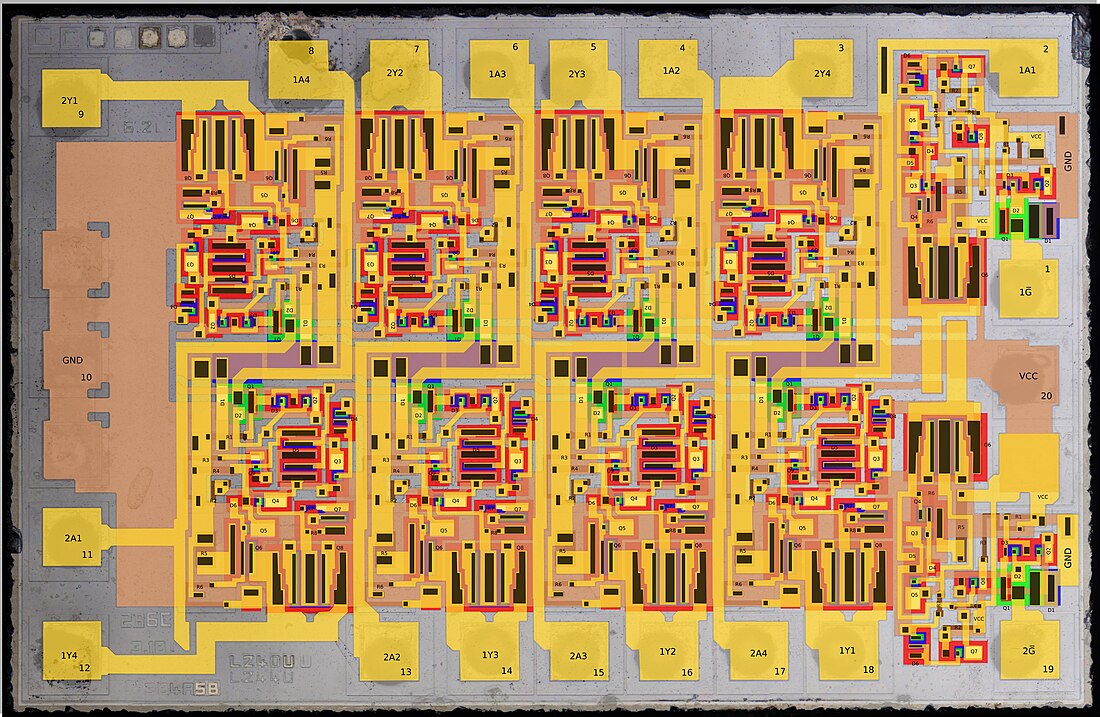

Il processo planare è una metodologia usata dall'industria dei semiconduttori per fabbricare parti individuali di un transistor, che a sua volta verrà poi connesso con altri transistor. Odiernamente è il metodo principale per la fabbricazione dei circuiti integrati. Il processo fu sviluppato da Jean Hoerni[1][2], conosciuto come uno dei Traitorous Eight, mentre lavorava presso la Fairchild Semiconductor, rilasciando un primo brevetto nel 1959.

Il concetto chiave era quello di considerare un circuito bi-dimensionalmente (un piano), permettendo lo sviluppo fotografico di pellicole negative, mascherando così la proiezione di luce dell'esposizione chimica. Ciò ha permesso l'utilizzo di una serie di esposizioni su un substrato (silicio) per la produzione di ossido di silicio (isolanti) o regioni drogate (conduttori). Grazie a metallizzazione (per unire circuiti integrati) e all'isolamento giunzione p-n (Kurt Lehovec), i ricercatori di Fairchild riuscirono a creare circuiti su un'unica fetta di silicio (wafer), partendo da una goccia di silicio monocristallino.

Il processo prevede le procedure di base per l'ossidazione del biossido di silicio (o silice) (SiO2), l'incisione e la diffusione del calore di SiO2. La fase finale prevede l'ossidazione dell'intero wafer con uno strato SiO2, l'incisione del contatto con i transistor e la copertura dell'ossido con un foglio di metallo, che permette ai transistor di rimanere collegati senza necessità di intervenire collegandoli manualmente.

Remove ads

Note

Voci correlate

Collegamenti esterni

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads