トップQs

タイムライン

チャット

視点

PA-RISC

ウィキペディアから

Remove ads

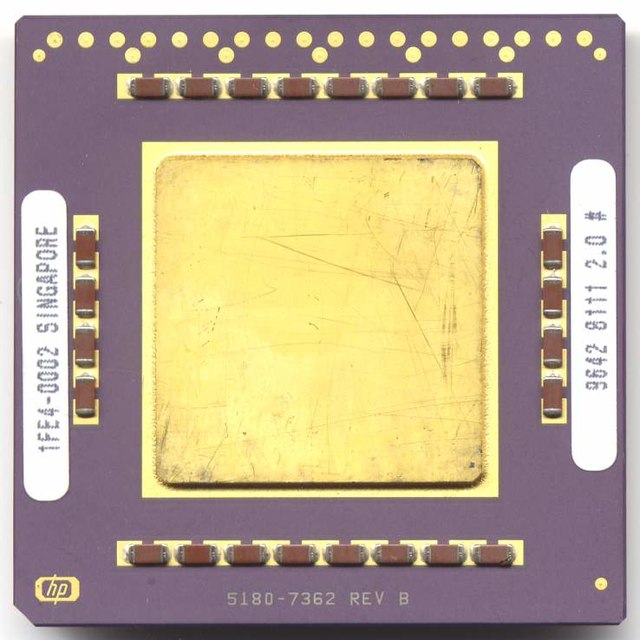

PA-RISC(ぴーえーりすく)は、ヒューレット・パッカード社 (HP) のSystems & VLSI Technology Operationが開発したマイクロプロセッサ アーキテクチャである。

その名前にも含まれているようにRISCアーキテクチャの実装であり、PAはPrecision Architecture(精密なアーキテクチャ)の略である。また、HP/PAつまりHewlett Packard Precision Architectureと呼ばれることもある。

1986年2月26日、PA-RISCの最初の実装であるTS1を採用した HP 3000 Series 930 と HP 9000 Model 840 が発表された[1][2]。

HPとインテルは Itanium(IA-64 ISA)を共同開発し、PA-RISCはItaniumに取って代わられた[3]。2008年末にはPA-RISCベースの HP 9000 システムの販売を終了したが、サポートは2013年まで継続予定である[4]。

Remove ads

背景

1980年代後半、HPはCISCのCPUを使った4つのコンピュータシリーズを製造していた。1つは80286ベースのPC/AT互換機 Vectra シリーズだが、残る3つはインテルベースではない。1つはアポロコンピュータ社を買収した際に得たモトローラの68000ファミリを使ったUNIXワークステーション HP Series 300 で、残る2つは Silicon-on-sapphire (SOS) 技術を使ったHP独自設計の 16ビットCPUのHP3000シリーズと、独自設計のFOCUSマイクロプロセッサを使ったUNIXワークステーションの HP 9000 シリーズ(16ビットおよび32ビット)である。HPはこれらPC互換機以外のマシンをPA-RISCを用いてひとつの RISC CPU ファミリに統合しようとしていた。

Precision Architecture は1986年に登場した。当初、32ビットの整数レジスタを32本と64ビットの浮動小数点レジスタを16本持っていた。浮動小数点レジスタが16本では性能に悪影響があることがわかり、バージョン1.1で倍の32本にしている。設計を行ったアーキテクトは、Allen Baum、Hans Jeans、Michael J. Mahon、Ruby Bei-Loh Lee、Russel Kao、Steve Muchnick、Terrence C. Miller、David Fotland、William S. Worley らである[5]。

Remove ads

PA-7000シリーズ

初期のPA-RISCチップは32ビットであった。最初の実装TS1は、TTL (74F) チップを組合わせてCPUを構成したものである。その後、VLSIを使ったマルチチップ方式となり、NMOSプロセス(NS1とNS2)とCMOSプロセスのもの(CS1とPCX)が作られた。1980年代終盤、そういった初期のPA-RISCチップがHP3000シリーズの新しいマシン930と950に使われた。これらのマシンは当時、開発した研究所の名前をとってSpectrumと呼ばれた。OSはMPE/iXが動作した。HP 9000シリーズもすぐにPA-RISCプロセッサを導入し、OSはHP製UNIXのHP-UXであった。

PA-RISCプロセッサ上に移植された他のオペレーティング・システムとしては、Mach、Linux、OpenBSD、NetBSD、NEXTSTEP、そしてリリースされなかったWindows NTがある。

PA-RISCの興味深い点は、そのシリーズのほとんどがL2キャッシュを持たなかったことである。その代わり大きな一次キャッシュを使っているが、以前は別チップをバスで接続していたが、現在は内蔵している。PA-7100LCとPA-7300LCだけがL2キャッシュを持つ。もうひとつPA-RISC独自と言えるのは7100LCで初めて導入された"Multimedia Acceleration eXtensions (MAX)"形式のマルチメディア命令 (SIMD) である。

Remove ads

PA-8000シリーズ

要約

視点

1996年、ISAが64ビットに拡張され、PA-RISC 2.0 と名付けられた。積和演算も追加されており、浮動小数点を多用するアルゴリズムで役立つ。MAX SIMD 拡張も備えており、マルチメディア・アプリケーションで役立つ命令を提供している。最初の PA-RISC 2.0 の実装は1996年1月、PA-8000 としてリリースされた。PA-8000は10個の機能ユニットを持ち、先進的なパイプラインシステムを搭載していた。また、命令キャッシュをふたつに分け、長期保持のキャッシュと短期保持のキャッシュを設けた。1997年にリリースされたPA-8200はPA-8000とほぼ同じであるが、分岐予測機能が改善され、TLBミス率が低減され、大容量高速キャッシュを持っていた。

PA-8500では1.5Mバイトの一次キャッシュをチップ上に組み込み、大きな性能向上を実現した。また、同時にDDRバスを導入し、最大2GB/sのメモリ転送速度を実現した。分岐予測のための履歴テーブルは2倍の2048エントリとなり、TLBは120エントリから160エントリに拡張された。

8600は8500の高クロック版であり、"quasi-LRU instruction cache eviction policy"(擬似LRU命令キャッシュ入れ替えポリシー)を採用している。8700は8600をさらに高クロックにして、2.25MBの一次キャッシュを持っている。また、擬似LRU命令キャッシュ入れ替えポリシー(命令キャッシュの中で最も使われていないエントリを見つけて入れ替える方式。本当に使用頻度を記録するのは至難なので「擬似」的に使用頻度を決める)とデータプリフェッチ機能(ロード命令を実行する前に、メモリから読み込んでくる)を備えている。一次キャッシュは大容量であるもののあまり速くなく、性能の足かせとなった。しかし、プロセスのサイズを考慮するとHPが内蔵したキャッシュのサイズは印象的である。

PA-8800(コードネームMako)は2つの独立したマクロプロセッサをひとつのダイに組み込んでいる。そして、ひとつのチップで2ウェイのSMPを構成する。8800内の各プロセッサは1.5Mバイトの一次キャッシュを持つが、HPは一次キャッシュのみというポリシーをやめて32MBの外部L2キャッシュをサポートした。外部バスは6.4GB/sのItanium2のバスを採用し、PA-RISCとItaniumに共通のサーバデザインを採用した。

PA-8900は8800によく似ているが、L2キャッシュを64MBまで拡張し、キャッシュエラー検出や訂正などの機能を強化した。噂されていたような8800のダイ縮小版ではない。これがPA-RISCシリーズの最後のマイクロプロセッサである。

HP社の方針と思われるが、PA-RISCは高性能であるものの周辺を含めたシステムとしての販売のみを行ってきたため、MIPSのように広く使われることはなかった。PA-RISCは既にその役目を終え、MIPSのように組み込みプロセッサとして残ることはない。

モデルの変遷

Remove ads

脚注・出典

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads