상위 질문

타임라인

채팅

관점

메모리 셀

위키백과, 무료 백과사전

Remove ads

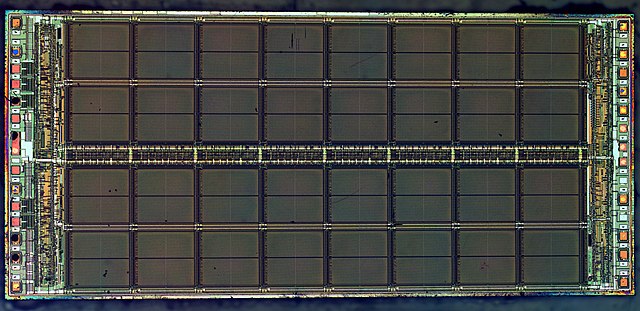

메모리 셀(memory cell)은 주기억장치의 기본적인 구성 요소이다. 메모리 셀은 1비트의 이진 정보를 저장하는 전자 회로이며, 논리 1(높은 전압 레벨)을 저장하도록 설정하고 논리 0(낮은 전압 레벨)을 저장하도록 재설정해야 한다. 그 값은 설정/재설정 프로세스에 의해 변경될 때까지 유지/저장된다. 메모리 셀의 값은 읽기를 통해 접근할 수 있다.

컴퓨터 역사를 통틀어 코어 메모리와 버블 메모리를 포함한 다양한 메모리 셀 아키텍처가 사용되었다. 오늘날 가장 일반적인 메모리 셀 아키텍처는 MOS 메모리이며, 이는 금속 산화물 반도체(MOS) 메모리 셀로 구성된다. 현대의 랜덤 액세스 메모리(RAM)는 MOS 전계 효과 트랜지스터(MOSFET)를 플립플롭으로 사용하며, 특정 유형의 RAM에는 MOS 축전기를 사용한다.

SRAM(정적 RAM) 메모리 셀은 일반적으로 MOSFET을 사용하여 구현되는 일종의 플립플롭 회로이다. 이들은 접근하지 않을 때 저장된 값을 유지하는 데 매우 낮은 전력을 필요로 한다. 두 번째 유형인 DRAM(동적 RAM)은 MOS 축전기를 기반으로 한다. 축전기를 충전 및 방전하여 셀에 '1' 또는 '0'을 저장할 수 있다. 그러나 축전기의 전하가 천천히 소산되기 때문에 주기적으로 새로 고쳐야 한다. 이러한 리프레시 프로세스로 인해 DRAM은 더 많은 전력을 소비하지만 더 높은 저장 밀도를 달성할 수 있다.

반면, 대부분의 비휘발성 메모리(NVM)는 플로팅 게이트 메모리 셀 아키텍처를 기반으로 한다. EPROM, EEPROM, 플래시 메모리와 같은 비휘발성 메모리 기술은 플로팅 게이트 MOSFET 트랜지스터에 의존하는 플로팅 게이트 메모리 셀을 활용한다.

Remove ads

설명

메모리 셀은 메모리의 기본 구성 요소이다. 이는 바이폴라, MOS 및 기타 반도체 소자와 같은 다양한 기술을 사용하여 구현할 수 있다. 또한 자기 재료(예: 페라이트 코어 또는 자기 버블)로도 만들 수 있다.[1] 사용된 구현 기술에 관계없이 이진 메모리 셀의 목적은 항상 동일하다. 이는 셀을 읽어서 접근할 수 있는 1비트의 이진 정보를 저장하며, 1을 저장하도록 설정하고 0을 저장하도록 재설정해야 한다.[2]

중요성

메모리 셀이 없는 논리 회로를 조합 논리라고 하며, 출력은 현재 입력에만 의존한다. 그러나 메모리는 디지털 시스템의 핵심 요소이다. 컴퓨터에서는 프로그램과 데이터를 모두 저장할 수 있으며, 메모리 셀은 나중에 디지털 시스템에서 사용될 조합 회로의 출력을 임시로 저장하는 데도 사용된다. 메모리 셀을 사용하는 논리 회로를 순차 회로라고 하며, 출력은 현재 입력뿐만 아니라 과거 입력의 기록에도 의존한다. 과거 입력 기록에 대한 이러한 의존성은 이러한 회로를 상태성으로 만들며, 이 상태를 저장하는 것은 메모리 셀이다. 이러한 회로는 작동을 위해 타이밍 생성기 또는 클록이 필요하다.[3]

대부분의 현대 컴퓨터 시스템에 사용되는 컴퓨터 메모리는 주로 DRAM 셀로 구성된다. 레이아웃이 SRAM보다 훨씬 작기 때문에 더 조밀하게 집적되어 더 저렴하고 용량이 더 큰 메모리를 생산할 수 있다. DRAM 메모리 셀은 축전기의 전하로 값을 저장하며, 전류 누설 문제가 있기 때문에 그 값을 지속적으로 다시 써야 한다. 이것이 DRAM 셀이 더 큰 SRAM(정적 RAM) 셀보다 느린 이유 중 하나이다. SRAM 셀은 그 값이 항상 사용 가능하다. 이것이 SRAM 메모리가 현대 마이크로프로세서 칩에 포함된 온-칩 캐시에 사용되는 이유이다.[4]

Remove ads

역사

요약

관점

1946년 12월 11일, 프레디 윌리엄스는 128개의 40비트 워드를 저장하는 자신의 음극선관(CRT) 저장 장치(윌리엄스관)에 대한 특허를 출원했다. 이 장치는 1947년에 작동되었으며, 랜덤 액세스 메모리(RAM)의 최초의 실용적인 구현으로 간주된다.[5] 같은 해, 자기코어 메모리에 대한 최초의 특허 출원이 프레데릭 비헤에 의해 제출되었다.[6][7] 실용적인 자기코어 메모리는 1948년 왕안에 의해 개발되었고, 1950년대 초반 제이 포레스터와 얀 A. 라이크만에 의해 개선된 후, 1953년 Whirlwind 컴퓨터와 함께 상용화되었다.[8] 켄 올슨 또한 그 개발에 기여했다.[9]

반도체 메모리는 1960년대 초반 바이폴라 트랜지스터로 만들어진 바이폴라 메모리 셀로 시작되었다. 성능은 향상되었지만 자기코어 메모리의 낮은 가격과 경쟁할 수 없었다.[10]

MOS 메모리 셀

1957년, 프로쉬와 데릭은 벨 연구소에서 최초의 이산화규소 전계 효과 트랜지스터를 제조할 수 있었는데, 이는 드레인과 소스가 표면에 인접한 최초의 트랜지스터였다.[11] 이후 1960년 벨 연구소에서 한 팀이 작동하는 MOSFET을 시연했다.[12][13] MOSFET의 발명은 이전에 자기 코어가 수행하던 기능인 금속 산화물 반도체(MOS) 트랜지스터를 메모리 셀 저장 요소로 실용적으로 사용할 수 있게 했다.[14]

최초의 현대 메모리 셀은 1964년 존 슈미트가 최초의 64비트 p-채널 MOS(PMOS) 정적 RAM(SRAM)을 설계하면서 도입되었다.[15][16]

SRAM은 일반적으로 6개의 트랜지스터 셀을 가지는 반면, DRAM(동적 랜덤 액세스 메모리)은 일반적으로 단일 트랜지스터 셀을 가진다.[17][15] 1965년, 도시바의 Toscal BC-1411 전자 계산기는 저마늄 바이폴라 트랜지스터와 콘덴서로 구성된 개별 메모리 셀에 180비트 데이터를 저장하는 형태의 정전식 바이폴라 DRAM을 사용했다.[18][19] MOS 기술은 현대 DRAM의 기반이다. 1966년, 로버트 H. 데나드는 IBM 토머스 J. 왓슨 연구 센터에서 MOS 메모리 연구를 진행하고 있었다. MOS 기술의 특성을 조사하던 중, 그는 MOS 기술이 축전기를 만들 수 있으며, MOS 축전기에 전하를 저장하거나 저장하지 않는 것이 비트의 1과 0을 나타낼 수 있고, MOS 트랜지스터가 축전기에 전하를 쓰는 것을 제어할 수 있음을 발견했다. 이는 그가 단일 트랜지스터 DRAM 메모리 셀을 개발하게 된 계기가 되었다.[20] 1967년, 데나드는 MOS 기술을 기반으로 한 단일 트랜지스터 DRAM 메모리 셀에 대한 특허를 출원했다.[21]

최초의 상업용 바이폴라 64비트 SRAM은 1969년 인텔에 의해 3101 쇼트키 TTL과 함께 출시되었다. 1년 후, MOS 기술을 기반으로 한 최초의 DRAM 집적 회로 칩인 인텔 1103을 출시했다. 1972년까지 반도체 메모리 판매에서 이전 기록을 깼다.[22] 1970년대 초 DRAM 칩은 3개 트랜지스터 셀을 사용했으며, 1970년대 중반부터 단일 트랜지스터 셀이 표준이 되었다.[17][15]

RCA는 1968년 288비트 CMOS SRAM 메모리 칩을 출시하여 CMOS 메모리를 상용화했다.[23] CMOS 메모리는 처음에는 1970년대 컴퓨터에서 더 널리 사용되던 NMOS 메모리보다 느렸다.[24] 1978년 히타치는 3 µm 공정으로 제조된 HM6147(4 kb SRAM) 메모리 칩과 함께 트윈웰 CMOS 공정을 도입했다. HM6147 칩은 당시 가장 빠른 NMOS 메모리 칩과 성능을 맞출 수 있었으며, HM6147은 또한 훨씬 적은 전력을 소비했다. 비슷한 성능과 훨씬 적은 전력 소비로 트윈웰 CMOS 공정은 1980년대 컴퓨터 메모리에서 가장 일반적인 반도체 제조 공정으로 NMOS를 결국 추월했다.[24]

1980년대 이후 가장 흔한 두 가지 유형의 DRAM 메모리 셀은 트렌치-커패시터 셀과 스택드-커패시터 셀이었다.[25] 트렌치-커패시터 셀은 실리콘 기판에 구멍(트렌치)을 만들고, 그 측벽이 메모리 셀로 사용되는 반면, 스택드-커패시터 셀은 3차원 셀 구조에서 메모리 셀이 수직으로 쌓이는 가장 초기 형태의 3차원 메모리(3D 메모리)이다.[26] 둘 다 1984년 히타치가 트렌치-커패시터 메모리를, 후지쯔가 스택드-커패시터 메모리를 도입하면서 처음 등장했다.[25]

플로팅 게이트 MOS 메모리 셀

플로팅 게이트 MOSFET(FGMOS)은 1967년 강대원과 사이먼 쩌가 벨 연구소에서 발명했다.[27] 그들은 FGMOS 트랜지스터를 사용하여 재프로그래밍 가능한 ROM(읽기 전용 메모리)을 만들 수 있는 플로팅 게이트 메모리 셀 개념을 제안했다.[28] 플로팅 게이트 메모리 셀은 나중에 EPROM(지울 수 있는 프로그래밍 가능 ROM), EEPROM(전기적으로 지울 수 있는 프로그래밍 가능 ROM) 및 플래시 메모리를 포함한 비휘발성 메모리(NVM) 기술의 기반이 되었다.[29]

플래시 메모리는 1980년 도시바의 마스오카 후지오에 의해 발명되었다.[30][31] 마스오카와 그의 동료들은 1984년 NOR 플래시의 발명을 발표했고,[32] 이어서 1987년 NAND 플래시를 발표했다.[33] 다중 레벨 셀(MLC) 플래시 메모리는 NEC가 1996년 64Mb 플래시 칩에 셀당 2비트를 저장하는 쿼드 레벨 셀을 시연하면서 도입되었다.[25] 플래시 메모리 셀이 3D 전하 트랩 플래시(CTP) 기술을 사용하여 수직으로 쌓이는 3D V-NAND는 2007년 도시바에 의해 처음 발표되었고,[34] 2013년 삼성전자에 의해 처음 상업적으로 제조되었다.[35][36]

Remove ads

구현

다음 회로도는 메모리 셀에 가장 많이 사용되는 세 가지 구현 방식을 자세히 설명한다.

- 동적 랜덤 액세스 메모리 셀(DRAM)

- 정적 랜덤 액세스 메모리 셀(SRAM)

- 아래에 보이는 J/K와 같이 논리 게이트만 사용하는 플립플롭

|  |  |

동작

요약

관점

DRAM 메모리 셀

저장

읽기

- 읽기를 위해 워드 라인(2)은 nMOS 트랜지스터(3)의 게이트에 논리 1(높은 전압)을 인가하여 전도성이 되게 하고, 축전기(4)에 저장된 전하는 비트 라인(1)으로 전송된다. 비트 라인은 기생 용량(5)을 가지며, 이는 전하의 일부를 소모시키고 읽기 프로세스를 늦출 것이다. 비트 라인의 용량은 저장 축전기(4)의 필요한 크기를 결정할 것이다. 이것은 트레이드오프이다. 저장 축전기가 너무 작으면 비트 라인의 전압이 너무 많은 시간을 들여 상승하거나 비트 라인 끝의 증폭기가 필요로 하는 임계값을 넘지 못할 수도 있다. 읽기 프로세스는 저장 축전기(4)의 전하를 저하시키므로 각 읽기 후 그 값은 다시 쓰인다.[38]

쓰기

SRAM 메모리 셀

(A) S = 1, R = 0: 세트

(B) S = 0, R = 0: 유지

(C) S = 0, R = 1: 리셋

(D) S = 1, R = 1: 허용되지 않음

제한된 조합 (D)에서 (A)로의 전환은 불안정한 상태로 이어진다.

저장

- SRAM 메모리 셀의 작동 원리는 트랜지스터 M1에서 M4를 논리 게이트로 그리면 더 쉽게 이해할 수 있다. 이렇게 하면 셀 저장이 두 개의 교차 연결된 인버터를 사용하여 구축된다는 것이 분명하다. 이 간단한 루프는 양안정 회로를 생성한다. 첫 번째 인버터 입력의 논리 1은 그 출력에서 0이 되고, 이 0은 두 번째 인버터로 전달되어 이 논리 0을 다시 논리 1로 변환하여 첫 번째 인버터의 입력으로 동일한 값을 다시 피드백한다. 이는 시간이 지나도 변하지 않는 안정적인 상태를 생성한다. 마찬가지로 회로의 다른 안정적인 상태는 첫 번째 인버터 입력에 논리 0을 가지는 것이다. 두 번 반전된 후에도 동일한 값을 다시 피드백할 것이다.[39]

- 따라서 회로가 존재할 수 있는 안정적인 상태는 단 두 가지이다.

- = 0 및 = 1

- = 1 및 = 0

읽기

쓰기

- 쓰기 프로세스는 유사하다. 차이점은 이제 메모리 셀에 저장될 새로운 값이 비트 라인()으로 구동되고, 그 반전된 값은 그 보수()로 구동된다는 것이다. 다음으로 트랜지스터 M5와 M6은 워드 라인()에 논리 1(높은 전압)을 구동하여 열린다. 이는 비트 라인을 안정적인 인버터 루프에 효과적으로 연결한다. 두 가지 가능한 경우가 있다.

- 루프의 값이 구동되는 새로운 값과 동일하면 변경이 없다.

- 루프의 값이 구동되는 새로운 값과 다르면 두 가지 상충되는 값이 있다. 비트 라인의 전압이 인버터의 출력을 덮어쓰려면 M5와 M6 트랜지스터의 크기가 M1-M4 트랜지스터보다 커야 한다. 이는 첫 번째 트랜지스터를 통해 더 많은 전류가 흐르게 하여 전압을 새로운 값의 방향으로 기울게 하며, 특정 시점에서 루프는 이 중간 값을 전체 전압으로 증폭한다.[39]

플립플롭

플립플롭은 다양한 구현 방식을 가지고 있으며, 그 저장 요소는 일반적으로 NAND 게이트 루프 또는 NOR 게이트 루프와 클록킹을 구현하는 데 사용되는 추가 게이트로 구성된 래치이다. 그 값은 항상 출력으로 읽을 수 있다. 값은 설정 또는 재설정 프로세스를 통해 변경될 때까지 저장된 상태로 유지된다. 플립플롭은 일반적으로 MOSFET을 사용하여 구현된다.

플로팅 게이트

플로팅 게이트 메모리 셀은 플로팅 게이트 MOSFET을 기반으로 하며, EPROM, EEPROM, 플래시 메모리를 포함한 대부분의 비휘발성 메모리(NVM) 기술에 사용된다.[29] R. Bez와 A. Pirovano에 따르면 다음과 같다.

플로팅 게이트 메모리 셀은 기본적으로 MOS 트랜지스터로, 게이트는 유전체로 완전히 둘러싸여 있으며(그림 1.2), 플로팅 게이트(FG)는 용량성 결합 제어 게이트(CG)에 의해 전기적으로 제어된다. 전기적으로 격리되어 있으므로 FG는 셀 장치의 저장 전극 역할을 한다. FG에 주입된 전하는 그곳에 유지되어 셀 트랜지스터의 '겉보기' 문턱 전압(즉, CG에서 본 VT)을 조절할 수 있다.[29]

Remove ads

같이 보기

각주

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads