상위 질문

타임라인

채팅

관점

PMOS 논리

위키백과, 무료 백과사전

Remove ads

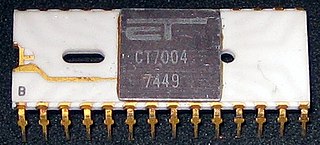

PMOS 또는 pMOS 로직(PMOS logic), pMOS 논리(p-채널 금속 산화물 반도체에서 유래)는 p-채널, 향상형 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)에 기반한 디지털 회로의 한 종류이다. 1960년대 후반과 1970년대 초반에 PMOS 논리는 대규모 집적회로의 지배적인 반도체 기술이었으나, 이후 NMOS 및 CMOS 소자에 의해 대체되었다.

역사 및 응용

요약

관점

모하메드 아탈라와 강대원은 1959년 벨 연구소에서 최초의 작동하는 MOSFET을 제조했다.[1] 그들은 PMOS와 NMOS 소자 모두를 제작했지만 PMOS 소자만 작동했다.[2] 제조 공정의 오염물(특히 나트륨)이 실제적인 NMOS 소자를 제조할 수 있을 만큼 충분히 잘 관리되기까지는 10년 이상이 걸릴 것이다.

당시 집적 회로에 사용할 수 있는 유일한 다른 소자인 접합형 트랜지스터와 비교할 때, MOSFET은 여러 가지 장점을 제공한다:

- 유사한 정밀도의 반도체 소자 제작 공정을 가정할 때, MOSFET은 접합형 트랜지스터 면적의 10%만을 필요로 한다.[3](pp. 87) 주요 이유는 MOSFET이 자체 절연되어 있어 칩 상의 인접 부품으로부터 p–n 접합 분리를 필요로 하지 않기 때문이다.

- MOSFET은 공정 단계가 적어 제조가 더 간단하고 저렴하다 (접합형 공정의 4단계[3](pp. 50)와 비교하여 확산 도핑 단계 1회[3](pp. 87)).

- MOSFET은 정적인 게이트 전류가 없으므로 MOSFET 기반 집적 회로의 전력 소비가 더 낮을 수 있다.

양극 집적회로에 비해 단점은 다음과 같다:

제너럴 마이크로일렉트로닉스는 1964년에 최초의 상용 PMOS 회로를 선보였다. 120개의 MOSFET을 갖춘 20비트 쉬프트 레지스터로, 당시에는 놀라운 수준의 집적도였다.[5] 1965년에 제너럴 마이크로일렉트로닉스가 빅터 컴퓨토미터용 전자 계산기를 위해 23개의 맞춤형 집적회로 세트를 개발하려 시도했으나[5] 당시 PMOS 회로의 신뢰성을 고려할 때 너무 야심찬 시도였고 결국 제너럴 마이크로일렉트로닉스의 몰락을 가져왔다.[6] 다른 회사들은 대규모 시프트 레지스터(제너럴 인스트루먼트)[7] 또는 아날로그 멀티플렉서 3705(페어차일드 반도체)[8]와 같이 당시 양극성 기술로는 구현하기 어려운 PMOS 회로를 계속 제조했다.

1968년 폴리실리콘 자체 정렬 게이트 기술 도입으로 큰 발전이 이루어졌다.[9] 페어차일드 반도체의 톰 클라인과 페데리코 파진은 자체 정렬 게이트 공정을 개선하여 상업적으로 실현 가능하게 만들었고, 그 결과 최초의 실리콘 게이트 집적 회로인 아날로그 멀티플렉서 3708이 출시되었다.[9] 자체 정렬 게이트 공정은 더욱 정밀한 제조 허용 오차를 가능하게 하여 더 작은 MOSFET과 감소되고 일관된 게이트 캐패시턴스를 모두 제공했다. 예를 들어, PMOS 메모리의 경우 이 기술은 칩 면적의 절반으로 3~5배 빠른 속도를 제공했다.[9] 폴리실리콘 게이트 소재는 자체 정렬 게이트를 가능하게 했을 뿐만 아니라 문턱 전압을 낮추어 최소 전원 공급 전압을 낮추었다 (예: -16 V[10](p. 1–13)), 전력 소비를 줄였다. 더 낮은 전원 공급 전압 때문에 실리콘 게이트 PMOS 로직은 종종 이전의 금속 게이트 PMOS와 달리 저전압 PMOS로 불린다.[3](pp. 89)

여러 가지 이유로 페어차일드 반도체는 관련된 관리자들이 원했던 만큼 PMOS 집적 회로 개발에 적극적으로 나서지 않았다.[11](pp. 1302) 그중 두 명인 고든 무어와 로버트 노이스는 1968년에 대신 자신의 스타트업인 인텔을 설립하기로 결정했다. 그들은 곧 페데리코 파진과 레스 바다츠를 포함한 다른 페어차일드 엔지니어들에 합류했다. 인텔은 1969년에 256비트 용량의 최초 PMOS 정적 랜덤 액세스 메모리인 인텔 1101을 선보였다.[11](pp. 1303) 1024비트 동적 랜덤 액세스 메모리인 인텔 1103은 1970년에 출시되었다.[12] 1103은 상업적인 성공을 거두었고 컴퓨터에서 자기 코어 메모리를 빠르게 대체하기 시작했다.[12] 인텔은 1971년에 최초의 PMOS 마이크로프로세서인 인텔 4004를 선보였다. 여러 회사가 인텔을 따랐다. 대부분의 초기 마이크로프로세서는 PMOS 기술로 제조되었다: 인텔의 4040과 8008; 내셔널 세미컨덕터의 IMP-16, PACE 및 SC/MP; 텍사스 인스트루먼트의 TMS1000; 로크웰 인터내셔널의 PPS-4[13] 및 PPS-8[14]. 이 마이크로프로세서 목록에는 여러 상업적인 최초의 제품이 포함되어 있다: 최초의 4비트 마이크로프로세서 (4004), 최초의 8비트 마이크로프로세서 (8008), 최초의 단일 칩 16비트 마이크로프로세서 (PACE), 그리고 최초의 단일 칩 4비트 마이크로컨트롤러 (TMS1000; CPU와 동일한 칩에 ROM).

1972년에는 마침내 NMOS 기술이 상업용 제품에 사용될 수 있는 수준까지 개발되었다. 인텔(2102)[15]과 IBM[12] 모두 1 kbit 메모리 칩을 선보였다. NMOS MOSFET의 n형 채널에서의 전자 이동도는 PMOS MOSFET의 p형 채널에서의 정공 이동도보다 약 3배 빠르므로 NMOS 로직은 스위칭 속도를 높일 수 있다. 이러한 이유로 NMOS 로직은 PMOS 로직을 빠르게 대체하기 시작했다. 1970년대 후반까지 NMOS 마이크로프로세서가 PMOS 프로세서를 추월했다.[16] PMOS 로직은 저렴한 비용과 단순 계산기 및 시계와 같은 응용 분야에 대한 상대적으로 높은 집적도로 인해 한동안 사용되었다. CMOS 기술은 PMOS 또는 NMOS보다 훨씬 낮은 전력 소비를 약속했다. 비록 1963년에 프랭크 완라스[17]가 이미 CMOS 회로를 제안했고, 1968년에 RCA의 상업용 4000 시리즈 CMOS 집적 회로가 생산에 들어갔지만, CMOS는 제조가 복잡했고 PMOS나 NMOS의 집적도나 NMOS의 속도를 따라잡지 못했다. CMOS가 마이크로프로세서의 주요 기술로 NMOS를 대체하기까지는 1980년대가 되어서야 했다.

Remove ads

설명

PMOS 회로는 NMOS 및 CMOS 대안과 비교하여 여러 가지 단점이 있다. 여기에는 여러 가지 다른 전원 전압(양수 및 음수 모두), 도통 상태에서의 높은 전력 소모, 그리고 상대적으로 큰 특징이 포함된다. 또한 전체적인 스위칭 속도가 더 낮다.

PMOS는 p형 (+) 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)를 사용하여 논리 게이트 및 기타 디지털 회로를 구현한다. PMOS 트랜지스터는 n형 트랜지스터 바디에 반전층을 생성하여 작동한다. p채널이라고 불리는 이 반전층은 정공을 p형 "소스" 및 "드레인" 단자 사이로 전도할 수 있다.

p 채널은 게이트라고 불리는 세 번째 단자에 음수 전압(-25V가 일반적[18])을 가하여 생성된다. 다른 MOSFET과 마찬가지로 PMOS 트랜지스터는 차단(또는 하부 문턱), 삼극관, 포화(때때로 활성이라고도 함), 속도 포화의 네 가지 작동 모드를 갖는다.

PMOS 논리는 설계 및 제조가 쉽지만(MOSFET은 저항으로 작동하도록 만들 수 있으므로 전체 회로를 PMOS FET로 만들 수 있다), 여러 가지 단점도 있다. 가장 큰 문제는 "풀업 네트워크"(PUN)가 활성 상태일 때, 즉 출력이 높을 때마다 PMOS 논리 게이트를 통해 직류(DC)가 흐른다는 것이다. 이는 회로가 유휴 상태일 때도 정적 전력 소모로 이어진다.

또한 PMOS 회로는 high에서 low로 전환하는 속도가 느리다. low에서 high로 전환할 때 트랜지스터는 낮은 저항을 제공하고 출력에서의 용량성 충전은 매우 빠르게 축적된다(매우 낮은 저항을 통해 축전기를 충전하는 것과 유사하다). 하지만 출력과 음수 전원 레일 사이의 저항은 훨씬 크므로 high에서 low로의 전환은 더 오래 걸린다(높은 저항을 통해 축전기를 방전하는 것과 유사하다). 더 낮은 값의 저항을 사용하면 프로세스 속도가 빨라지지만 정적 전력 소모도 증가한다.

또한, 비대칭적인 입력 로직 레벨은 PMOS 회로를 노이즈에 취약하게 만든다.[19]

대부분의 PMOS 집적 회로는 17-24볼트 직류 전원 공급 장치를 필요로 한다.[20] 그러나 인텔 4004 PMOS 마이크로프로세서는 금속 게이트 대신 폴리실리콘을 사용하는 PMOS 로직을 사용하여 더 작은 전압 차이를 허용한다. TTL 신호와의 호환성을 위해 4004는 양수 전원 전압 VSS=+5V와 음수 전원 전압 VDD = -10V를 사용한다.[21]

Remove ads

게이트

p형 MOSFET은 로직 게이트 출력과 양수 전원 전압 사이에 이른바 "풀업 네트워크"(PUN)로 배열되어 있으며, 로직 게이트 출력과 음수 전원 전압 사이에는 저항이 배치되어 있다. 회로는 원하는 출력이 높을 경우 PUN이 활성화되어 양수 전원과 출력 사이에 전류 경로를 형성하도록 설계된다.

PMOS 게이트는 모든 전압이 반전되면 NMOS 게이트와 동일한 배열을 갖는다.[22] 따라서 액티브-하이 로직의 경우, 드 모르간의 법칙은 PMOS NOR 게이트가 NMOS NAND 게이트와 동일한 구조를 가지며 그 반대도 마찬가지임을 보여준다.

|

|

|

각주

더 읽어보기

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads