Najlepsze pytania

Chronologia

Czat

Perspektywa

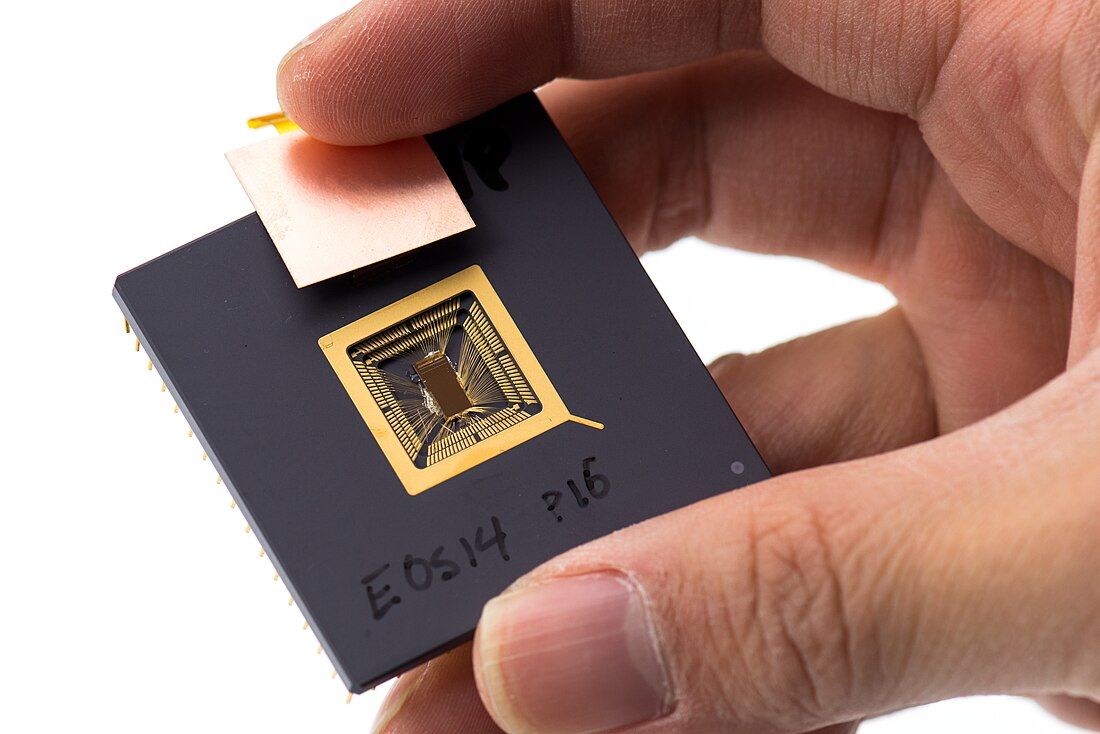

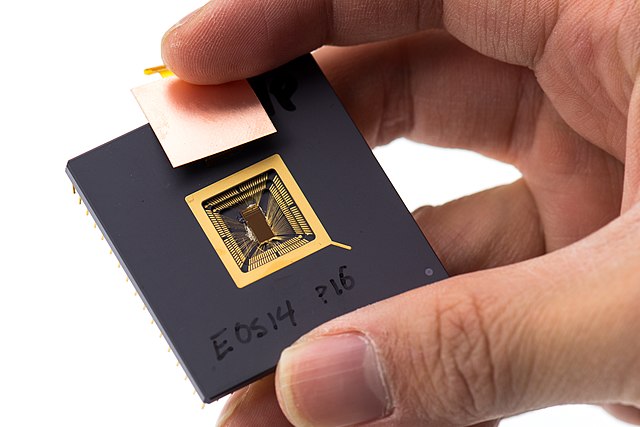

RISC-V

Z Wikipedii, wolnej encyklopedii

Remove ads

RISC-V – otwarta architektura zestawu instrukcji procesora (ISA) oparta na zasadach RISC.

W odróżnieniu od większości ISA, RISC-V może być swobodnie używany w dowolnym celu, umożliwiając każdemu projektowanie, produkcję i sprzedaż czipów i oprogramowania RISC-V. Chociaż nie jest pierwszą otwartą architekturą ISA[1] ma duże znaczenie, ponieważ został zaprojektowany z myślą o nowoczesnych skomputeryzowanych urządzeniach, takich jak ogromne chmury obliczeniowe, wysokiej klasy telefony komórkowe i najmniejsze systemy wbudowane. Takie zastosowania wymagają zarówno wydajności, jak i efektywności energetycznej. Architektura ta ma także obszerne wsparcie programistyczne, co pozwala uniknąć typowego problemu nowych architektur procesorowych.

Projekt rozpoczął się w 2010 r. na Uniwersytecie Kalifornijskim w Berkeley, ale wielu współtwórców to wolontariusze i pracownicy z branży pracujący poza uniwersytetem[2].

RISC-V ISA został zaprojektowany z myślą o małych, szybkich i energooszczędnych implementacjach w świecie rzeczywistym[3][4], ale bez nadmiernego projektowania dla konkretnego stylu mikroarchitektury[4].

7 maja 2017 zostały opublikowane wersja 2.2 ISA przestrzeni użytkownika oraz wersja robocza 1.10 uprzywilejowanego ISA[4][5][6][7].

Remove ads

Zobacz też

- RISC

- openRISC

Przypisy

Linki zewnętrzne

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads