Top Qs

Linha do tempo

Chat

Contexto

Heterogeneous System Architecture

Da Wikipédia, a enciclopédia livre

Remove ads

Heterogeneous System Architecture (HSA) é um conjunto de especificações de vários fornecedores que permite a integração de unidades centrais de processamento e processadores gráficos no mesmo barramento, com memória e tarefas compartilhadas.[1] O HSA está sendo desenvolvido pela HSA Foundation, que inclui (entre muitos outros) AMD e ARM. O objetivo declarado da plataforma é reduzir a latência de comunicação entre CPUs, GPUs e outros dispositivos de computação e tornar esses vários dispositivos mais compatíveis da perspectiva do programador,[2]:3[3] aliviando o programador da tarefa de planejar a movimentação de dados entre memórias disjuntas de dispositivos (como deve ser feito atualmente com OpenCL ou CUDA).[4]

CUDA e OpenCL, bem como a maioria das outras linguagens de programação bastante avançadas, podem usar HSA para aumentar seu desempenho de execução. A computação heterogênea é amplamente utilizada em dispositivos de sistema em chip, como tablets, smartphones, outros dispositivos móveis e consoles de videogame.[5] O HSA permite que os programas usem o processador gráfico para cálculos de ponto flutuante sem memória ou agendamento separado.[6]

Remove ads

Justificativa

A lógica por trás do HSA é aliviar a carga dos programadores ao transferir cálculos para a GPU. Originalmente impulsionada exclusivamente pela AMD e chamada de FSA, a ideia foi estendida para abranger unidades de processamento além de GPUs, como DSPs de outros fabricantes.

- Etapas executadas ao descarregar cálculos para a GPU em um sistema não HSA

- Etapas executadas ao descarregar cálculos para a GPU em um sistema HSA, usando a funcionalidade HSA

As GPUs modernas são muito adequadas para executar instruções únicas, vários dados (SIMD) e instruções únicas, vários threads (SIMT), enquanto as CPUs modernas ainda estão sendo otimizadas para ramificação. etc.

Remove ads

Visão geral

Resumir

Perspectiva

Originalmente introduzido por sistemas embarcados como o Cell Broadband Engine, o compartilhamento de memória do sistema diretamente entre vários participantes do sistema torna a computação heterogênea mais comum. A computação heterogênea em si se refere a sistemas que contêm múltiplas unidades de processamento – unidades centrais de processamento (CPUs), unidades de processamento gráfico (GPUs), processadores de sinais digitais (DSPs) ou qualquer tipo de circuito integrado específico para aplicações (ASICs). A arquitetura do sistema permite que qualquer acelerador, por exemplo, um processador gráfico, opere no mesmo nível de processamento que a CPU do sistema.

Entre seus principais recursos, o HSA define um espaço de endereço virtual unificado para dispositivos de computação: enquanto as GPUs tradicionalmente têm sua própria memória, separada da memória principal (CPU), o HSA exige que esses dispositivos compartilhem tabelas de páginas para que os dispositivos possam trocar dados compartilhando ponteiros. Isso deve ser suportado por unidades de gerenciamento de memória personalizadas.[2]:6–7 Para tornar a interoperabilidade possível e também facilitar vários aspectos da programação, o HSA foi criado para ser independente de ISA tanto para CPUs quanto para aceleradores, e para oferecer suporte a linguagens de programação de alto nível.

Até agora, as especificações do HSA abrangem:

Camada intermediária HSA

HSAIL (Heterogeneous System Architecture Intermediate Language), um conjunto de instruções virtuais para programas paralelos

- semelhante à LLVM Intermediate Representation e SPIR (usado por OpenCL e Vulkan)

- finalizado para um conjunto de instruções específico por um compilador JIT

- tomar decisões tardias sobre quais núcleos devem executar uma tarefa

- explicitamente paralelo

- suporta exceções, funções virtuais e outros recursos de alto nível

- suporte para depuração

Modelo de memória HSA

- compatível com modelos de memória C++11, OpenCL, Java e .NET

- consistência relaxada

- projetado para oferecer suporte a linguagens gerenciadas (por exemplo, Java) e não gerenciadas (por exemplo, C)

- tornará muito mais fácil desenvolver compiladores de terceiros para uma ampla gama de produtos heterogêneos programados em Fortran, C++, C++ AMP, Java, et al.

Despachante HSA e tempo de execução

- projetado para permitir enfileiramento de tarefas heterogêneo: uma fila de trabalho por núcleo, distribuição de trabalho em filas, balanceamento de carga por roubo de trabalho

- qualquer núcleo pode agendar trabalho para qualquer outro, incluindo ele mesmo

- redução significativa da sobrecarga de trabalho de agendamento para um núcleo

Os dispositivos móveis são uma das áreas de aplicação do HSA, na qual ele produz maior eficiência energética.[5]

Diagramas de blocos

As ilustrações abaixo comparam a coordenação CPU-GPU sob HSA em comparação com arquiteturas tradicionais.

- Arquitetura padrão com uma GPU discreta conectada ao barramento PCI Express. A cópia zero entre a GPU e a CPU não é possível devido às memórias físicas distintas.

- O HSA traz memória virtual unificada e facilita a passagem de ponteiros pelo PCI Express em vez de copiar todos os dados.

- Na memória principal particionada, uma parte da memória do sistema é alocada exclusivamente para a GPU. Como resultado, a operação de cópia zero não é possível.

- Memória principal unificada, onde GPU e CPU são habilitados para HSA. Isso torna possível a operação de cópia zero.[7]

- A MMU da CPU e a IOMMU da GPU devem estar em conformidade com as especificações de hardware HSA.

Remove ads

Suporte de software

Resumir

Perspectiva

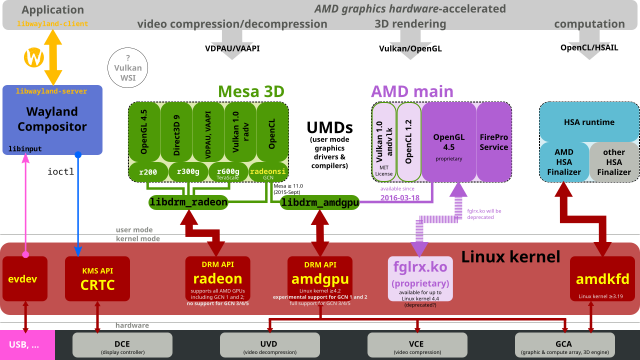

Alguns dos recursos específicos do HSA implementados no hardware precisam ser suportados pelo kernel do sistema operacional e por drivers de dispositivo específicos. Por exemplo, o suporte para placas de vídeo AMD Radeon e AMD FirePro, e APUs baseadas no Graphics Core Next (GCN), foi incorporado à versão 3.19 do kernel principal do Linux, lançada em 8 de fevereiro de 2015.[9] Os programas não interagem diretamente com amdkfd, mas enfileiram seus trabalhos utilizando o tempo de execução do HSA.[10] Esta primeira implementação, conhecida como amdkfd, foca em APUs "Kaveri" ou "Berlin" e funciona junto com o driver gráfico do kernel Radeon existente.

Adicionalmente, amdkfd oferece suporte ao heterogeneous queuing (HQ), que visa simplificar a distribuição de trabalhos computacionais entre várias CPUs e GPUs da perspectiva do programador. O suporte para gerenciamento de memória heterogênea (HMM), adequado apenas para hardware gráfico com a versão 2 do IOMMU da AMD, foi aceito na versão principal do kernel Linux 4.14.[11]

O suporte integrado para plataformas HSA foi anunciado para o lançamento "Sumatra" do OpenJDK, previsto para 2015.[12]

O AMD APP SDK é um kit de desenvolvimento de software proprietário da AMD voltado para computação paralela, disponível para Microsoft Windows e Linux. Bolt é uma biblioteca de modelos C++ otimizada para computação heterogênea.[13]

O GPUOpen abrange algumas outras ferramentas de software relacionadas ao HSA. A versão 2.0 do CodeXL inclui um profiler HSA.[14]

Suporte de hardware

Resumir

Perspectiva

AMD

Em fevereiro de 2015, apenas as APUs da série A "Kaveri" da AMD (cf. processadores para desktop "Kaveri" e processadores dispositivos móveis "Kaveri") e o PlayStation 4 da Sony permitiam que a GPU integrada acessasse a memória por meio da versão 2 do IOMMU da AMD. APUs anteriores (Trinity e Richland) incluíam a funcionalidade do IOMMU da versão 2, mas apenas para uso por uma GPU externa conectada via PCI Express.[carece de fontes]

As APUs Carrizo e Bristol Ridge posteriores a 2015 também incluem a funcionalidade IOMMU versão 2 para a GPU integrada.[carece de fontes]

A tabela a seguir mostra recursos das APUs da AMD

- Para modelos Excavator FM2+: A8-7680, A6-7480 e Athlon X4 845.

- Um PC seria um nó.

- Uma APU combina uma CPU e uma GPU. Ambos têm núcleos.

- Requer suporte de firmware

- No SSE4. No SSSE3.

- O desempenho de precisão simples é calculado a partir da velocidade de clock do núcleo base (ou boost) com base em uma operação FMA.

- Shaders unificados : unidades de mapeamento de textura : unidades de saída de renderização

- Para reproduzir conteúdo de vídeo protegido, também é necessário suporte a placa, sistema operacional, driver e aplicativo. Um monitor HDCP compatível também é necessário para isso. O HDCP é obrigatório para a saída de certos formatos de áudio, colocando restrições adicionais na configuração multimídia.

- Para reproduzir conteúdo de vídeo protegido, também é necessário suporte a placa, sistema operacional, driver e aplicativo. Um monitor HDCP compatível também é necessário para isso. O HDCP é obrigatório para a saída de certos formatos de áudio, colocando restrições adicionais na configuração multimídia.

- Para alimentar mais de dois monitores, os painéis adicionais devem ter suporte nativo para DisplayPort.[24] Alternativamente, adaptadores DisplayPort-to-DVI/HDMI/VGA ativos podem ser empregados.

- DRM (Direct Rendering Manager) é um componente do kernel Linux. O suporte nesta tabela refere-se à versão mais atual.

- DRM (Direct Rendering Manager) é um componente do kernel Linux. O suporte nesta tabela refere-se à versão mais atual.

ARM

A microarquitetura Bifrost da ARM, conforme implementada no Mali-G71,[29] é totalmente compatível com as especificações de hardware HSA 1.1. Em junho de 2016, a ARM não anunciou suporte de software que usaria esse recurso de hardware.

Remove ads

Ver também

Referências

- Tarun Iyer (30 de abril de 2013). «AMD Unveils its Heterogeneous Uniform Memory Access (hUMA) Technology». Tom's Hardware. Consultado em 30 de abril de 2025

- George Kyriazis (30 de abril de 2025). Heterogeneous System Architecture: A Technical Review (PDF) (Relatório). AMD. Arquivado do original (PDF) em 28 de março de 2014

- «What is Heterogeneous System Architecture (HSA)?». AMD. Consultado em 30 de abril de 2025. Arquivado do original em 21 de junho de 2014

- Joel Hruska (26 de agosto de 2013). «Setting HSAIL: AMD explains the future of CPU/GPU cooperation». ExtremeTech. Ziff Davis. Consultado em 30 de abril de 2025

- «Heterogeneous System Architecture: Purpose and Outlook». gpuscience.com. 9 de novembro de 2012. Consultado em 30 de abril de 2025. Cópia arquivada em 1 de fevereiro de 2014

- «Heterogeneous system architecture: Multicore image processing using a mix of CPU and GPU elements». Embedded Computing Design. Consultado em 30 de abril de 2025. Cópia arquivada em 26 de março de 2013

- «Kaveri microarchitecture». SemiAccurate. 15 de janeiro de 2014

- Michael Larabel (21 de julho de 2014). «AMDKFD Driver Still Evolving For Open-Source HSA On Linux». Phoronix. Consultado em 30 de abril de 2025

- «Linux kernel 3.19, Section 1.3. HSA driver for AMD GPU devices». kernelnewbies.org. 8 de fevereiro de 2015. Consultado em 30 de abril de 2025

- «HSA-Runtime-Reference-Source/README.md at master». github.com. 14 de novembro de 2014. Consultado em 30 de abril de 2025

- «Linux Kernel 4.14 Announced with Secure Memory Encryption and More». 13 de novembro de 2017. Consultado em 30 de abril de 2025. Arquivado do original em 13 de novembro de 2017

- Alex Woodie (26 de agosto de 2013). «HSA Foundation Aims to Boost Java's GPU Prowess». HPCwire. Consultado em 30 de abril de 2025

- «Bolt on github». GitHub. 11 de janeiro de 2022. Consultado em 30 de abril de 2025

- AMD GPUOpen (19 de abril de 2016). «CodeXL 2.0 includes HSA profiler». Consultado em 30 de abril de 2025. Arquivado do original em 27 de junho de 2018

- «AMD Announces the 7th Generation APU: Excavator mk2 in Bristol Ridge and Stoney Ridge for Notebooks». 31 de maio de 2016. Consultado em 17 de setembro de 2022

- «AMD Mobile "Carrizo" Family of APUs Designed to Deliver Significant Leap in Performance, Energy Efficiency in 2015» (Nota de imprensa). 20 de novembro de 2014. Consultado em 17 de setembro de 2022. Cópia arquivada em 10 de fevereiro de 2015

- «The Mobile CPU Comparison Guide Rev. 13.0 Page 5 : AMD Mobile CPU Full List». TechARP.com. Consultado em 17 de setembro de 2022

- «AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver». VideoCardz.com. Consultado em 17 de setembro de 2022

- Cutress, Ian (1 de fevereiro de 2018). «Zen Cores and Vega: Ryzen APUs for AM4 – AMD Tech Day at CES: 2018 Roadmap Revealed, with Ryzen APUs, Zen+ on 12nm, Vega on 7nm». Anandtech. Consultado em 17 de setembro de 2022

- Larabel, Michael (17 de novembro de 2017). «Radeon VCN Encode Support Lands in Mesa 17.4 Git». Phoronix. Consultado em 19 de setembro de 2022

- «AMD Ryzen 5000G 'Cezanne' APU Gets First High-Res Die Shots, 10.7 Billion Transistors In A 180mm2 Package». wccftech. 12 de agosto de 2021. Consultado em 19 de setembro de 2022

- Tony Chen; Jason Greaves, «AMD's Graphics Core Next (GCN) Architecture» (PDF), AMD, consultado em 19 de setembro de 2022

- «A technical look at AMD's Kaveri architecture». Semi Accurate. Consultado em 19 de setembro de 2022

- «How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?». AMD. Consultado em 19 de setembro de 2022. Cópia arquivada em 11 de dezembro de 2014

- Airlie, David (26 de novembro de 2009). «DisplayPort supported by KMS driver mainlined into Linux kernel 2.6.33». Consultado em 19 de setembro de 2022

- «Radeon feature matrix». freedesktop.org. Consultado em 19 de setembro de 2022

- Deucher, Alexander (16 de setembro de 2015). «XDC2015: AMDGPU» (PDF). Consultado em 19 de setembro de 2022

- Michel Dänzer (17 de novembro de 2016). «[ANNOUNCE] xf86-video-amdgpu 1.2.0». lists.x.org

- «ARM Bifrost GPU Architecture». 30 de maio de 2016. Consultado em 30 de abril de 2025

Remove ads

Ligações externas

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads