热门问题

时间线

聊天

视角

簽核

来自维基百科,自由的百科全书

Remove ads

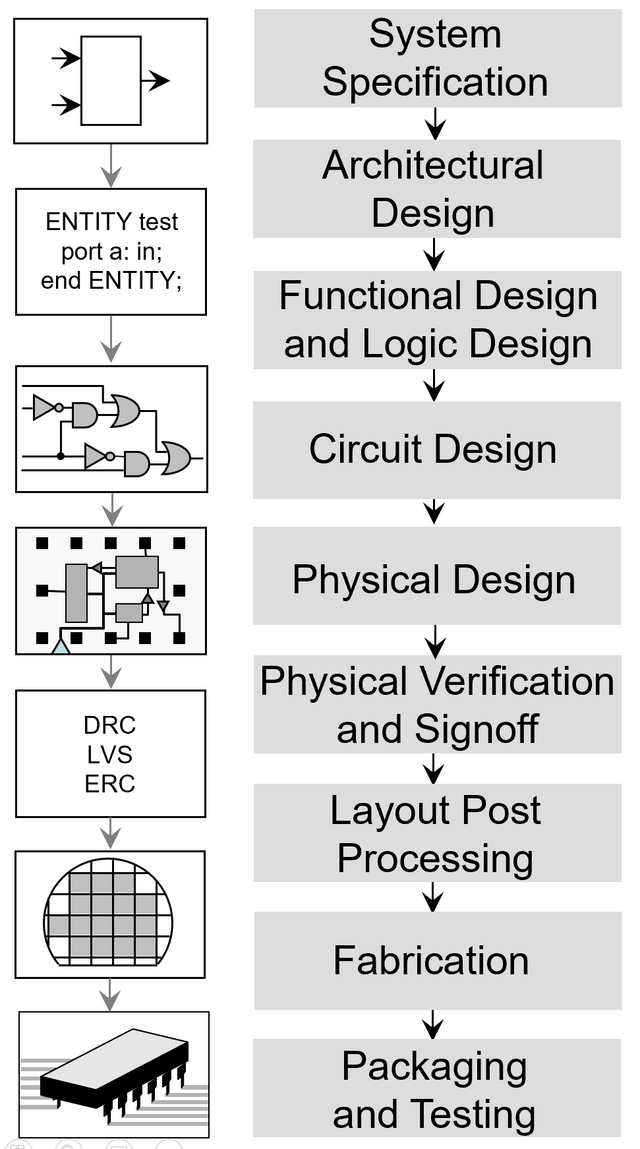

簽核(signoff,sign-off)檢查在積體電路設計自動化中,是指設計在可以下線之前必須通過的一系列驗證步驟的統稱。 這意味著一個迭代過程,涉及使用一種或多種檢查類型在各處進行增量修復,然後重新測試設計。 簽核分為兩類:前道簽核和後道簽核。 後道簽核之後,晶片進入製造。在列出規範中的所有特性後,驗證工程師會為這些特性編寫覆蓋率以識別缺陷,並將RTL設計返還給設計師。 缺陷可能包括與規範相比的缺失特性、設計錯誤(如筆誤和功能性錯誤)等。 當覆蓋率達到最大百分比時,驗證團隊將對其簽核。 通過採用像UVM、OVM或VMM這樣的驗證方法學,驗證團隊可以開發可復用的驗證環境。 目前UVM比其他方法更為流行。

歷史

在二十世紀六十年代末,像英特爾這樣的半導體公司工程師使用Rubylith來製作半導體微影光罩。 工程師手工繪製的半導體元件電路圖由熟練的原理圖繪製員手工轉移到D尺寸的犢皮紙上,以在光罩上製作元件的物理版圖。[1]:6

這些犢皮紙隨後由原工程師手工檢查並予以「簽核」;對原理圖的所有修改也會被記錄、檢查並再次「簽核」。[1]:6

檢查類型

隨著超大型積體電路設計接近22納米製程及更小製程節點,簽核檢查變得更加複雜,原因是先前被忽略或粗略近似的二階效應影響增大。 簽核檢查分為若干類別。

- 設計規則檢查(DRC)有時稱為幾何驗證。 它用於驗證在當前微影限制下設計是否可以可靠製造。 在先進製程節點,DFM規則從可選(以提高良率)升級為必需。

- 形式驗證將版圖後網表(包括任何由版圖驅動的優化)的邏輯功能與版圖前、綜合後的網表進行驗證。

- 電壓降分析 — 也稱為IR-drop分析。 此檢查驗證電源網格是否足夠強,以保證代表二進制高電平的電壓不會因數百萬電晶體的共同切換而跌落到低於電路可靠工作所需的裕度。

- 訊號完整性分析——分析由串擾等問題造成的雜訊,並檢查其對電路功能的影響,確保電容性毛刺不足以越過數據路徑上門的閾值電壓。

- 靜態時序分析(STA)正逐步被統計靜態時序分析(SSTA)取代。 STA用於驗證設計中所有邏輯數據路徑在目標時鐘頻率下能否工作,特別是在晶片製程變動影響下。 STA用作替代SPICE,因為SPICE類比的運行時間使其對現代設計的全晶片分析不可行。

- 電遷移壽命檢查——保證在目標時鐘頻率下操作時,電路不會因電遷移而失效,從而滿足最小壽命要求。

- 功能靜態簽核檢查——使用搜索和分析技術檢查所有可能的測試用例下的設計失敗;功能靜態簽核域包括時鐘域交叉、復位域交叉和 X 傳播。

- 功能靜態簽核檢查——使用搜索和分析技術在所有可能測試用例下檢查設計失效;功能性靜態簽核領域包括時鐘域跨越、復位域跨越和X傳播。

Remove ads

工具

一小部分工具被歸類為「金牌」或簽核級工具。 在不帶供應商偏見的情況下將工具歸類為簽核級,通常依靠試錯法,因為只有在設計製造出來後才能確定工具的準確性。 因此,一個常用(並常被工具廠商宣稱)的衡量指標是該工具促成的成功下線次數。 有人認為該指標不足、定義不清且對某些工具無關,尤其是那些僅在完整流程中起部分作用的工具。[2]

雖然廠商常誇大其工具套件在端到端(通常是從RTL到GDS對於ASIC,以及從RTL到時序收斂對於FPGA)執行上的便利, 大多數半導體設計公司仍然使用來自不同廠商的組合工具(常稱為「最佳」工具),以最小化片上和片後相關性誤差。[3] 由於獨立工具評估成本高昂(主要廠商如新思科技與Cadence的設計工具單一許可可能花費數萬到數十萬美元)且風險較大(如果在生產設計上評估失敗,會導致上市時程延遲),因此只有最大的設計公司(如英特爾、IBM、飛思卡爾和德州儀器)才有條件進行。 作為一種增值服務,若干半導體代工廠現在提供預評估的參考/推薦方法學(有時稱為「RM」流程),其中包含推薦工具、版本和用於在工具間移動數據並自動化整個流程的腳本清單。[4][5]

下列供應商和工具為代表性列舉,非詳盡:

- DRC/LVS - Mentor HyperLynx DRC Free/Gold 、 Mentor Calibre 、 Magma Quartz 、 Synopsys Hercules 、 Cadence Assura

- 電壓降分析 - Cadence Voltus 、 Apache Redhawk 、 Magma Quartz Rail

- 訊號完整性分析 - Cadence CeltIC (串擾雜訊)、 Cadence Tempus Timing Signoff Solution 、 Synopsys PrimeTime SI (串擾延遲/雜訊)、 Extreme-DA GoldTime SI (串擾延遲/雜訊)

- 靜態時序分析 - Synopsys PrimeTime 、 Magma Quartz SSTA 、 Cadence ETS 、 Cadence Tempus Timing Signoff Solution 、 Extreme-DA GoldTime

參考

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads