ARM

konkurenční technologie vývoje procesorů From Wikipedia, the free encyclopedia

Remove ads

ARM je v informatice označení architektury procesorů používaných díky své nízké spotřebě elektrické energie zejména v mobilních zařízeních (mobilní telefony, tablety), nyní však proniká i do PC[1]. Globálně je v roce 2013 ARM nejpočetněji zastoupenou architekturou mikroprocesorů,[2][3][4] přičemž 60 % mobilních zařízení na světě obsahuje ARM čip. V roce 2013 bylo vyrobeno 10 miliard ARM procesorů, v roce 2014 už 50 miliard.[5] Vývoj ARM architektury započal v Británii ve firmě ARM Holdings v 80. letech 20. století.

Remove ads

Historie

Firma ARM Holdings (dříve ARM Limited) používala dříve pro ARM architekturu obchodní název Advanced RISC Machine, původně pak Acorn RISC Machine. ARM architektura způsobila v několika směrech revoluci v informačních technologiích.[zdroj?] Je založen na architektuře RISC, neméně pozoruhodné je, že první procesory ARM byly založeny na GaAs polovodičích, které dovolily na tehdejší dobu velmi vysoké taktovací frekvence. Rovněž použitá 32bitová šířka slova nebyla v době vzniku ARM samozřejmostí. První mikroprocesor s architekturou ARM byl navržen firmou ARM Limited v roce 1984.

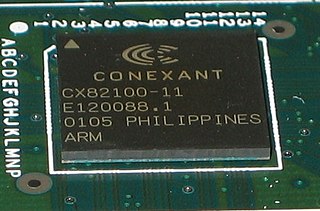

Firma ARM Holdings časem ustoupila od výroby procesorů a místo toho se soustředila pouze na jejich vývoj. Schéma procesorů ARM je tedy „intelektuálním vlastnictvím“ firmy ARM, která jej licencuje výrobcům hardware. Procesory ARM je dnes možné najít ve všech odvětvích spotřební elektroniky od PDA, mobilních telefonů, multimediálních přehrávačů, přenosných herních konzolí, kalkulaček až po počítačové periferie (pevné disky, routery). Procesory ARM mají ve svém výrobním programu desítky výrobců, ve spotřební elektronice se používají např. procesory XScale od firmy Marvell, nebo OMAP od firmy Texas Instruments.

V roce 2006 byla architektura ARM zastoupena v 98 % z více než jedné miliardy každoročně prodaných mobilů.[6]

Rostoucí význam architektury ARM, jejíž nejvýkonnější zástupci[7] dnes již mají dostatečný výkon i pro použití v osobních počítačích byl pravděpodobně jedním z impulsů, které přiměly firmu Intel k vývoji nízkopříkonových procesorů Intel Atom. Podle jiných zdrojů byl Intel Atom odpovědí na úsporné mikroprocesory AMD Geode.

Remove ads

Charakteristika

Architektura ARM se nejvýrazněji uplatňuje v mobilních zařízeních (mobilní telefony, tablety) a ve vestavěných systémech (pevný disk, USB flash disk, Wi-Fi čipy, routery apod.). Nízká spotřeba energie při vysokém výpočetním výkonu má zásadní význam hlavně v zařízeních napájených bateriemi, avšak je velkou výhodou také u zařízení pracujících v náročných tepelných podmínkách. Nízkopříkonové procesory totiž nepotřebují složité a přitom relativně nespolehlivé chlazení.

Remove ads

Přehled 32bitových procesorů ARM

Remove ads

Přehled 32bitových procesorů ARM (ARMv8)

Přehled 64bitových procesorů ARM (ARMv8)

Remove ads

Přehled procesorů ARMv9

Remove ads

Charakteristika architektury ARM

- přístup do paměti pouze instrukcemi Load/Store

- částečné překrývání vnitřních registrů

- možnost podmíněného vykonání instrukcí

- jednoduchý a výkonný instrukční soubor, jednoduše využitelné kompilátory vyšších programovacích jazyků

Procesory ARM podporují dva adresové módy. Můžeme adresovat buď prostřednictvím čítače instrukcí, nebo pomocí bázové adresy uložené v jednom z vnitřních registrů. Do paměti lze přistupovat pouze instrukcemi Load/Store (Load-Store Architecture) výrazně zjednodušuje výkonnou jednotku (Execution Unit) procesoru, protože pouze několik instrukcí pracuje přímo s pamětí. Většina instrukcí pracuje s vnitřními registry.

ARM procesory podporují dvě úrovně priority přerušení s dvěma zaměnitelnými bankami registrů. Nejkratší doba provedení požadavku na přerušení je poskytována režimem rychlého přerušení FIQ (Fast Interrupt Request). Druhý typ přerušení je IRQ (Interrupt Request), který se používá pro obsluhu přerušení nevyžadujících extrémně krátké doby odezvy nebo v případě, že vlastní obsluha přerušení je oproti době reakce procesoru mnohonásobně delší.

Architektura procesoru ARM

Procesor ARM obsahuje 44 základních instrukcí s jednotnou šířkou 32 bitů. V jednom taktu se vykonávají pouze instrukce pracující s aritmeticko-logickou jednotkou (ALU), s registry nebo s přímými operandy.

Procesor pracuje ve čtyřech základních režimech:

- uživatelský režim USR

- privilegovaný režim supervizora SUP

- privilegovaný režim přerušení IRQ

- privilegovaný režim rychlého přerušení FIQ

V procesoru je obsaženo 25 částečně se překrývajících 32bitových registrů (15 registrů je univerzálních a zbývajících 10 má speciální funkce), z toho 16 registrů je v každém režimu činnosti programově přístupných.

Registry R0 až R13 jsou přístupné v uživatelském režimu pro libovolný účel. Registr R14 je určen výhradně pro uživatelský režim. Pět registrů je speciálně určeno pro režim rychlého přerušení (FIQ). Je-li procesor v režimu FIQ, je těchto pět registrů mapováno do registrů R10 až R14. V registru R14 je uložena návratová adresa do přerušeného programu. Další dva registry jsou určeny pro režim přerušení (IRQ) a v tomto režimu překrývají registry R13 a R14 uživatelského režimu. Další dva registry jsou určeny pro privilegovaný režim supervizora. Poslední registr R15 obsahuje stavové slovo procesoru a čítač instrukcí, který je sdílen všemi režimy činnosti. Významově nejvyšších 6 bitů PSW obsahuje stav procesoru, dalších 24 bitů představuje čítač instrukcí a významově nejnižší dva bity obsahují aktuální režim činnosti procesoru.

Specifika procesoru ARM

Jak bylo uvedeno, procesor obsahuje množinu částečně se překrývajících registrů, takže v případě přerušení nemusí být proveden kompletní úklid registrů. V případě režimu rychlého přerušení FIQ je zkrácení doby odezvy procesoru dosaženo použitím čtyř lokálních univerzálních registrů a jednoho registru s návratovou adresou. Tyto registry mohou obsahovat všechny ukazatele a různé čítače používané v jednoduchých procedurách obsluhy vstupů a výstupů, takže lze dobře dosáhnout velmi rychlého opakovaného přepínání procesoru mezi uživatelským režimem a režimem „rychlého přerušení“.

Procesor je dále schopen obsloužit následující přerušení:

- chyba v adresování (Address Exception Trap)

- chyba při čtení, nebo zápisu dat do vnější paměti (Data Fetch Cyrcle Aborts)

- chyba při čtení instrukce z vnější paměti (Instruction Fetch Cyrcle Aborts)

- přerušení programovými prostředky (instrukce SWI)

- nedefinovaný kód instrukcí (Undefined Instruction Traps)

- reset procesoru

Procesor poskytuje 26bitovou adresu lineární operační paměti, což umožňuje adresovat 64 MiB fyzické paměti. Odkaz na data mimo rozsah způsobí přerušení chyby adresování (Address Exception Trap).

Instrukční soubor procesoru ARM

Instrukční soubor můžeme rozdělit na skupiny:

- instrukce zpracování údajů – zpracování registrových operandů, zpracování přímých operandů, nastavení podmínkového kódu a instrukce aritmeticko-logické

- instrukce jednoduchého přenosu údajů

- instrukce blokového přenosu údajů – instrukce vykonávají přenos mezi skupinou registrů a spojitou oblastí paměti, přičemž jeden registr je použit jako směrník

- instrukce větvení a větvení s uchováním návratové adresy (tyto instrukce odkládají PSW do R14)

- instrukce přechodu do privilegovaného režimu supervizora, které zahrnují i programové přerušení

Všechny instrukce mají čtyřbitový prefix, který zajišťuje podmíněné vykonání samotné instrukce. Instrukce zpracování údajů pracují pouze nad souborem vnitřních registrů a každá z těchto instrukcí obsahuje reference na tři operandy: jeden cílový a dva zdrojové.

Instrukce přenosu údajů jsou použity k přenosu dat mezi pamětí a souborem registrů (Load) a naopak (Store). Efektivní adresa je vypočtena součtem obsahu zdrojového registru a posuvu (offset) daného 12bitovou konstantou nebo obsahem dalšího registru. Posuv (offset) může být přičítán k indexovému registru nebo od něj odčítán. Instrukce přenosu údajů mohou pracovat jak s jednotlivými byty, tak s dvojitým slovem (Double Word, 32bitů). Byte přečtený z paměti je uložen do významově nejnižších 8bitů cílového registru a zbytek obsahu je zaplněn nulami.

Instrukce blokového přenosu zabezpečují přenos několika registrů jednou instrukcí. Instrukce obsahuje pole bitů, z nichž každý odpovídá jednomu registru viditelnému v daném režimu. Bit 0 odpovídá R0, bit 1 odpovídá R1, atd.

Instrukce programového přerušení jsou použity především pro přechod do privilegovaného režimu supervizora. PSW je ukládáno do registru R14 režimu supervizora a hodnota čítače instrukcí je dána adresou softwarového přerušení.

Velikost stránky paměti

ARMv8 (AArch64) má v 64bitovém režimu volitelnou velikost stránky paměti 4, 16 nebo 64 KiB. Standardní velikost je 4 KiB. Větší stránky paměti jsou používány v serverovém a HPC prostředí[61] a v systému Android 15,[62] kde 16 KiB stránky poskytují zvýšení výkonu o 5 až 10 % na úkor zvýšení využití operační paměti RAM o asi 9 %.

Remove ads

Odkazy

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads