トップQs

タイムライン

チャット

視点

RISC-V

オープンソースのCPU命令セットアーキテクチャ ウィキペディアから

Remove ads

RISC-V(リスク ファイブ)はカリフォルニア大学バークレー校で開発されオープンソースで提供されている命令セットアーキテクチャ(英: instruction set architecture、ISA)である[2]。

本稿ではISAであるRISC-Vの実装(RISC-Vコア)およびエコシステム(対応OS、開発ツール)を含めて解説する。

Remove ads

概要

オープンソースライセンス

他の多くの命令セットアーキテクチャ(ISA)設計とは異なり、RISC-V ISAは、使用料のかからないオープンソースライセンスで提供されている。多くの企業がRISC-Vハードウェアを提供したり、発表したりしており、RISC-Vをサポートするオープンソースのオペレーティングシステムが利用可能であり、いくつかの一般的なソフトウェアツールチェーンで命令セットがサポートされている。

命令セット(ISA)がRISC

RISC-Vは縮小命令セットコンピュータ (RISC) の原則に基づいている。RISC-V ISAの注目すべき特徴は、ロードストア・アーキテクチャ[3][4]、CPU内のマルチプレクサを簡素化するビットパターン、IEEE 754浮動小数点、アーキテクチャ的に中立な設計、符号拡張を高速化するために最上位ビットを固定位置に配置することなどである。命令セットは、幅広い用途に対応できるように設計されている。可変幅で拡張可能なので、常により多くのエンコーディングビットを追加することができる。32、64、128ビットの3つのワード幅と、さまざまなサブセットをサポートしている。各サブセットの定義は、3つのワード幅によって若干異なる。サブセットは、小型の組み込みシステム、パーソナルコンピュータ、ベクトルプロセッサを搭載したスーパーコンピュータ、倉庫規模の19インチラックマウント並列コンピュータをサポートしている。

命令セットスペースの拡張

ISAの128ビット伸張版の命令セットスペースが確保されたのは、60年にわたる業界の経験から、最も回復不可能な命令セット設計上の誤りはメモリに対するアドレス空間の不足であることが示されているからである。2016年時点で、128ビットISAは意図的に未定義のままであるが、これは、このような大規模なメモリシステムでの実用的な経験がまだほとんどないためである。

実用的な使用に使える設計

このプロジェクトは2010年にカリフォルニア大学バークレー校で開始されたが、貢献者の多くは大学とは関係のないボランティアである。他のアカデミックな設計は、一般的に説明を簡単にするためだけに最適化されているのに対し、RISC-Vの命令セットは、実用的なコンピュータで使用できるように設計されている。

2019年6月の時点で、ユーザスペースISAのバージョン2.2と特権ISAのバージョン1.11は凍結されており、ソフトウェアとハードウェアの開発を進めることができる。デバッグ仕様は、ドラフトとしてバージョン0.13.2が用意されている[5]。

Remove ads

開発動機

要約

視点

オープンなISA

命令セットアーキテクチャはコンピュータにおけるハードウェアとソフトウェアのインターフェースである。良いISA/インターフェースはソフトウェアの再利用性を上げコストを低減する。また、ハードウェア製造者間の競争が促進され、ハードウェア製造者は、より多くのリソースを設計に使えるようになり、ソフトウェア・サポートに使うリソースは少なくできる[6]。

これまでは商業的に成功し広く用いられていたISAはクローズドにライセンシングされてきた。たとえばARMホールディングスやミップス・テクノロジーズは、彼らの特許を利用するにあたり、相当のライセンス料を課する[7]。彼らはまた、設計の優位性や命令セットを記した文書を渡す前に秘密保持契約(NDA)を要求する。クローズドなISAおよびIPは改変を禁止されるケースが多く、性能向上を目的としたISAの改良や教育を目的としたISAの変更が妨げられていた。このような背景から、オープンかつフリーなISAには一定の需要があった。

RISC-V以前のオープンISAのほとんどはGNU General Public License(GPL)を使用し、ユーザーにコピーや利用するにあたって実装をオープンにするようにさせていた。RISC-Vでは自由に利用可能なCPUデザインをBSDライセンス下で提供することを目指している。BSDライセンスであれば、RISC-Vチップの設計や派生成果物の作成は、RISC-V自身と同様にオープンかつ自由にも、あるいは クローズドで独占的にもできる。

実用可能かつシンプルなISA

プロジェクトの主張によれば、命令セットの設計では新しい設計原理が現れることはほとんどなく、過去40年間で最も成功した設計はますます似通ってきている。失敗した設計のほとんどは、出資した企業が商業的に失敗したのであり、命令セットが技術的に劣っていたからではない。よって、よく設計されたオープンな命令セットが十分に確立された設計原理を用いて設計されたならば、多くのベンダーが長期間に渡ってサポートする気になるだろう[6]。

他の学術目的の設計とは異なり、RISC-V命令セットは、研究内容の説明のための簡略化に向けて最適化するのではなく、実用的なコンピュータに向けて最適化した簡略化にすると宣言されている。この簡略化はコンピュータの速度向上を目的とするが、コストや電力使用量も削減される。この命令セットに含まれるものは、ロード/ストア アーキテクチャ、CPU内部のマルチプレクサを単純化するビット・パターン、簡略化された標準に基づいた浮動小数点数、アーキテクチャに中立な設計、および、最上位の符号ビットを固定にすることで得られる符号拡張の高速化である。符号拡張は、しばしば、クリティカル・タイミング・パスになると言われている。

命令セットは3種類のワード幅

命令セットは、幅広い層のユーザー向けに設計されている。32-、64-、128-ビットの3つのワード幅、様々なサブセットをサポートする。各サブセットの定義は、3つワード幅間で、わずかに変化する。サブセットは、小さな組み込みシステム、パーソナルコンピュータ、ベクタプロセッサを持つスーパーコンピュータ、および、ウェアハウス・スケールのラック・マウント型並列計算マシンをサポートする。

命令セットは可変長幅

命令セットは、可変長幅で、拡張可能であるため、より多くのエンコード・ビットが追加可能である。ISAには128ビットまで拡張されたバージョンまで予約されている。これは、過去60年の業界の歴史の中で、過去の命令セットでメモリアドレス空間が不足していたことが原因で、取り返しのつかない失敗が起きたことを反映している。2016年現在、128-ビットのISAは、その巨大なメモリシステムに関する知見がほとんどないために、意図的に未定義にされている。

教育上も有効

RISC-Vのシンプルさは教育上有効でもある。整数命令のサブセットは単純であるため、学生が初歩的な練習をすることができ、整数命令サブセットはシンプルなISAであるため、ソフトウェアによる研究用マシンの制御にも利用できる。可変長のISAは、学生の練習と研究のための拡張を可能にする[8]。別定義の特権命令セットを用いれば、OSの研究を、コンパイラを再設計せずにサポートできる[9]。RISC-Vのオープンな知的財産によって、設計を公開したり、再利用したり、修正が可能になる[8]。

Remove ads

歴史

要約

視点

先行開発

「RISC」という用語は1980年頃に作られた[10]。それ以前は、よりシンプルな設計のコンピュータは効率的な可能性があるといういくつかの知見は存在したが、そのような設計指針はまだ広まってはいなかった。単純で効率的なコンピュータは、常に学術的な関心にとどまっていた。

研究者は、RISC命令セットのDLXを、1990年に初版の『コンピュータ・アーキテクチャ 設計・実現・評価の定量的アプローチ』のために作成した。著者のデイビッド・パターソンは、後にRISC-Vを支援した。しかし、DLXは教育目的用だったため、研究者やホビーストはDLXをFPGAを使って実装したが、商業的には成功しなかった。

ARM CPUのバージョン2とその前は、パブリックドメインの命令セットであり、現在もまだGNUコンパイラコレクションによってサポートされている。このISA向けに、3つのオープンソースのコアが存在するが、もはや製造されていない[11][12]。

OpenRISCは、DLXをベースとしたオープンソースのISAであり、RISCの実装の1つである。OpenRISCはGCCとLinuxの実装を完全にサポートしているが、商業的な実装は少ない。

RISC-Vという名称は、カリフォルニア大学バークレー校が発表したRISC ISAの5番目のメジャー・バージョンであることを表している[8]。RISC-Vの前の4つのバージョンは、それぞれRISC-I[13]、RISC-II[14]、SOAR[15]、およびSPUR[16]である。

RISC-V財団とRISC-V International

カリフォルニア大学バークレー校のクルステ・アサノヴィッチは、オープンソースのコンピュータシステムが広く普及している状況を認識していた。2010年、彼は「夏の3ヶ月の短期間プロジェクト」の中で、RISC-Vを開発、公開することを決意した。この計画は、研究者や企業のユーザーに役立つものだったため[6]、バークレー校のデイビッド・パターソンも協力した。もともとパターソンは、バークレーRISCの特性を定めた人物であり、RISC-Vは、彼のRISC-Vの研究プロジェクトの長い経歴の一つである。初期の開発では、DARPAが財政支援を行っていた[8]。

RISC-V財団は2015年に設立された[1]。RISC-V財団をサポートしている組織としては、アドバンスト・マイクロ・デバイセズ[17]、Andes Technology[18]、BAEシステムズ、Berkeley Architecture Research、Bluespec, Inc.、Cortus、Google、GreenWaves Technologies、ヒューレット・パッカード・エンタープライズ、華為技術、IBM、Imperas Software、中国科学院、IIT Madras、ラティスセミコンダクター、Mellanox Technologies、Microsemi、マイクロンテクノロジー、NVIDIA、NXPセミコンダクターズ、オラクル、クアルコム、Cryptography Research、ウェスタン・デジタル、SiFiveなどがある[19][20][21]。

2019年11月に、RISC-V財団は米国の貿易制限に対する懸念からスイスへの移転を表明し[22]、2020年3月にはスイスの国際交流協会RISC-V Internationalが設立された[1]。

RISC-V Internationalは、RISC-Vをソフトウェアおよびハードウェア設計に自由に利用できるようRISC-Vの仕様を公開している。仕様の策定はRISC-V Internationalの会員により行われる。さらに、会員組織は製品に対して「RISC-V Compatible™」ロゴの使用を許可される[23]。

表彰

- 2017年、Linley Groupにより、ベスト・テクノロジー(命令セット)賞に選定された。

実装

要約

視点

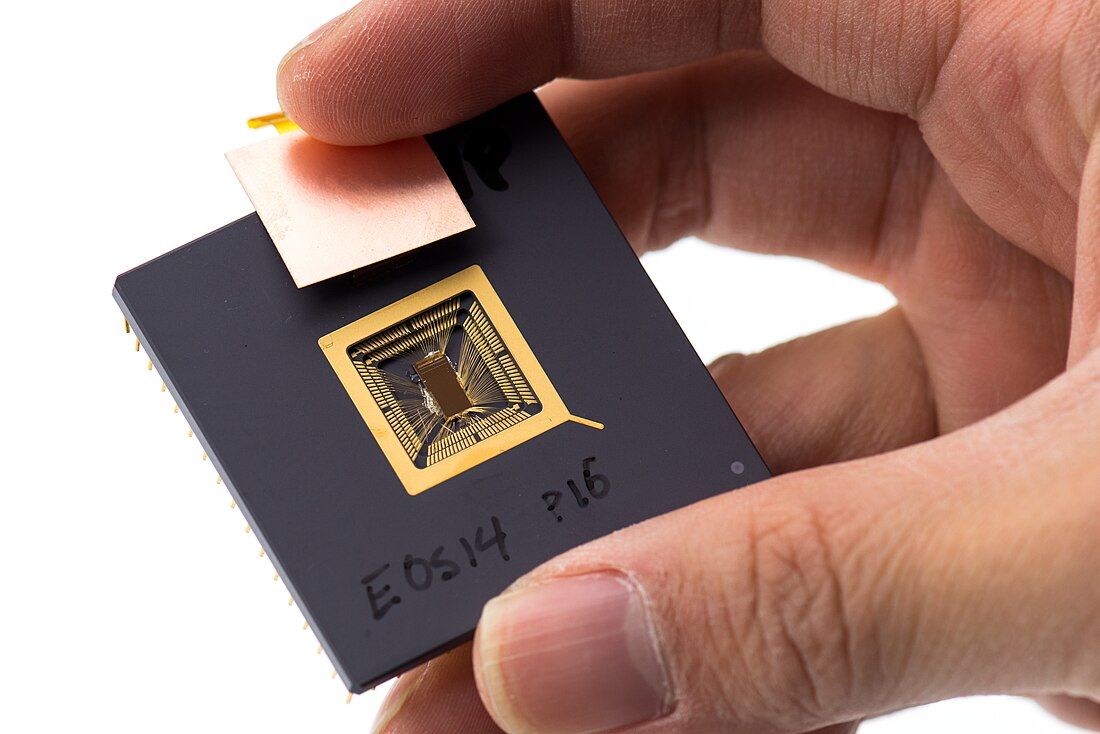

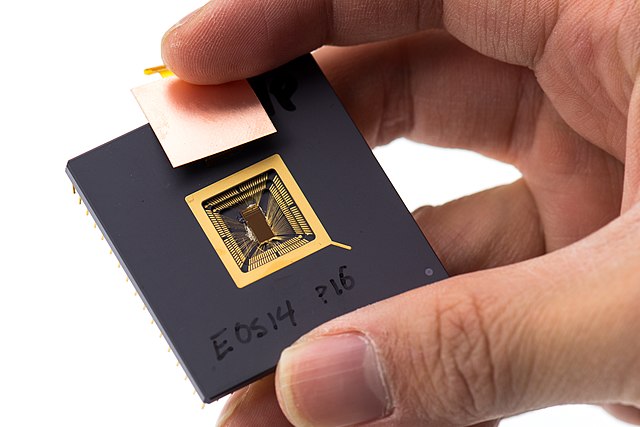

RISC-Vオーガニゼーションは、RISC-VのCPUとSoCの実装リストを管理している[24]。

既存

既存の商用実装には以下のようなものがある。

- Xuantie-910: 2019年7月発表[25]、アリババグループ (T-Head) による。2.5GHz 16コア64ビット(RV64GCV)、アウトオブオーダー型。2021年10月、T-Headはこれを含む4プロセッサ (C910[26], C906[27], E906[28], E902[29]) をオープンソース化した。

- N25/NX25: 2017年リリース、RISC-V Internationalの創設メンバーであるAndes Technology Corporationによる[30]

- CodasipとUltraSoCは、CodasipのRISC-VコアなどのIPとUltraSoCのデバッグ、最適化、アナリティクスを組み合わせたRISC-V組み込みSOC向けに完全にサポートされた知的財産を開発している[31]。

- GD32Vシリーズ: GigaDeviceによる[32]。RV32IMAC実装。中国の電子企業Sipeed社が製造したLongan Nanoボードに採用[33]。

- GAP8: 2018年2月発表、GreenWaves Technologiesによる。32ビット1コントローラ+8個のコンピュートコア、32ビットSoC(RV32IMC)。GAPuino GAP8開発ボードは2018年5月に出荷を開始[34][35][36]。

- SCR1: Syntacoreによる。RV32I/E[MC] 実装。

- UltraSOCは標準トレースシステムを提案し、実装を寄贈した。

- SweRV Core: 2018年12月発表、Western Digitalによる。インオーダー2ウェイスーパースカラと9ステージのパイプライン設計を特徴とする。WDは、SweRVベースのプロセッサをフラッシュコントローラやSSDに採用する予定で、2019年1月にサードパーティ向けにオープンソースとして公開している[37][38][39]。

- ESP32-S2 ULPコプロセッサ: Espressifによる。

開発環境

- IAR Systemsは、RV32 32ビットRISC-Vコアと拡張機能をサポートする「IAR Embedded Workbench for RISC-V」の最初のバージョンをリリースした。今後のリリースでは、64ビットのサポートとより小型のRV32Eベース命令セットのサポート、機能安全認証とセキュリティソリューションが含まれる予定。

- SEGGERは、同社のデバッグ・プローブJ-Link[40]、同社の統合開発環境Embedded Studio[41]、RTOSのembOSと組み込みソフトウェアにRISC-Vコアのサポートを追加した[42]。

- FPGAコアのインスタントSoCRISC-Vコア。C++で定義されたRISC-Vコアを含むSystem On Chip。

開発会社

- RISC-Vハードウェアの開発に特化して設立されたSiFiveは、2017年にリリースされたプロセッサモデルを持っている[43][44]。これらには、Linuxなどの汎用OSを実行可能なクアッドコア、64ビット(RV64GC)のシステムオンチップ(SoC)が含まれている[45]。

- CloudBEARは、さまざまなアプリケーション向けに独自のRISC-Vコアを開発するプロセッサIP企業である[46]。

- Syntacore[47]はRISC-V Internationalの創設メンバーであり、最初の商用RISC-V IPベンダーの1社である。2015年からRISC-V IPファミリーの開発とライセンス供与を行っている。2018年現在、製品ラインにはオープンソースのSCR1を含む8つの32コアと64ビットコアが含まれている[48]。2016年にはSyntacore IPをベースにした最初の商用SoCがデモされた[49]。

開発中

- ASTCは、組み込みIC用のRISC-V CPUを開発した[50]。

- Centre for Development of Advanced Computing, India(C-DAC)は、64ビットのアウトオブオーダーのクアッドコアRISC-Vプロセッサを開発している[51]。

- Cobham GaislerのNOEL-V 64ビット[52]。

- ケンブリッジ大学コンピューター研究所が、FreeBSDプロジェクトと共同で、そのオペレーティングシステムを64ビットRISC-Vに移植し、ハードウェア・ソフトウェア研究プラットフォームとして使用していると発表している。

- Esperanto Technologiesは、RISC-Vベースの高性能コア「ET-Maxion」、エネルギー効率の高いコア「ET-Minion」、グラフィックスプロセッサ「ET-Graphics」の3つのプロセッサを開発していると発表した[53]。

- チューリッヒ工科大学とボローニャ大学は、エネルギー効率の高いIoTコンピューティングのための並列超低電力(PULP)プロジェクトの一環として、オープンソースのRISC-V PULPinoプロセッサを共同開発した[54]。

- European Processor Initiative(EPI)、RISC-V Accelerator Stream。 [55][56]

- インド工科大学マドラス校は、IoT用の小型32ビットCPUから、RapidIOやHybrid Memory Cube技術をベースにしたサーバーファームなどの倉庫規模のコンピュータ向けに設計された大規模64ビットCPUまで、6つの用途に合わせて6つのRISC-VオープンソースCPU設計を開発している。

- lowRISCは、64ビットのRISC-V ISAをベースにした完全オープンソースのハードウェアSoCを実装する非営利プロジェクトである。

- Nvidiaは、GeForceグラフィックスカードのFalconプロセッサを置き換えるためにRISC-Vを使用する計画[57]。

- SiFiveは、同社初のRISC-Vアウトオブオーダー高性能CPUコア「U8シリーズプロセッサIP」を発表した[58]。

オープンソース

以下のように多くのオープンソースのRISC-V CPUの設計(IP)がある。

Remove ads

ソフトウェア

新しい命令セットの通常の問題は、CPU設計とソフトウェアの不足であり、この2つの問題はその使いやすさを制限し、採用を減少させる。RISC-Vのソフトウェアには、ツールチェーン、オペレーティングシステム、ミドルウェア[vague]、設計ソフトウェアなどがある。

新しい命令セットを作る際に一般的な問題点は、CPUの設計とソフトウェアが存在しないことである[要出典]。

現在利用可能なRISC-Vソフトウェアのツールとしては以下が挙げられる:

- GNU Compiler Collection(GCC)ツールチェーン(GDBおよびデバッカーを含む)

- LLVMツールチェーン

- OVPsim simulator(およびRISC-V Fast Processor Modelsのライブラリ)

- Spike simulator

- QEMU内のシミュレータ

UEFI仕様v2.7のRISC-Vバインディングおよびtianocoreへのポートは、HPEのエンジニアによって完了しており、アップストリームに反映されることが期待されている。seL4マイクロカーネルのポートも存在する[68][69]。ウェブブラウザ上でRISC-V Linuxが動作するシミュレータシステムがJavaScriptで書かれている[70]。

OSサポート

RISC-VではOSをサポートするために、ユーザーモード命令の仕様と汎用目的の特権命令セットの予備仕様が用意されている。OSのサポートはLinuxカーネル、FreeBSD、NetBSDに存在しているが、特権モード命令は2019年3月14日現在[update]は標準化されていない[71]ため、暫定的な対応となっている。RISC-Vアーキテクチャへの予備のFreeBSD移植版は2016年2月にアップストリームに反映され、FreeBSD 11.0で公開された[72][73]。Debianへのポート[74]およびFedoraへのポート[75]はすでに安定している。Das U-Bootへのポートが存在する[76]。

Remove ads

脚注

公開資料、解説書

関連項目

関連図書

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads