상위 질문

타임라인

채팅

관점

반도체 제조

반도체 소자, 일반적으로 집적 회로(IC)를 제조하는 데 사용되는 공정 위키백과, 무료 백과사전

Remove ads

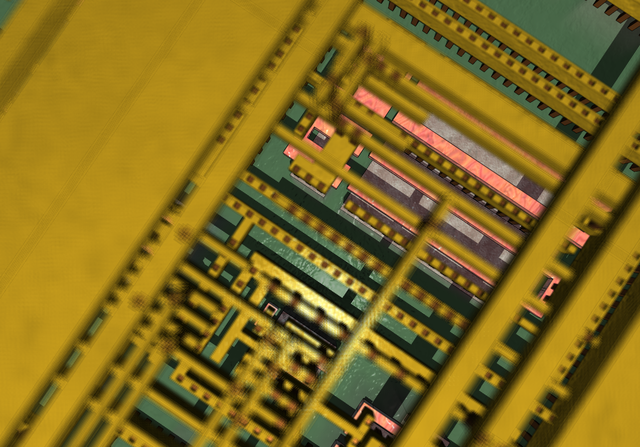

반도체 소자 제조(semiconductor device fabrication)는 일반적으로 마이크로프로세서, 마이크로컨트롤러 및 메모리(예: RAM 및 플래시 메모리)와 같은 집적 회로(IC)를 포함한 반도체 소자를 제조하는 공정이다. 이는 열 산화, 박막 증착, 이온 주입, 식각과 같은 단계와 함께 다단계 포토리소그래피 및 물리화학적 공정이며, 이 과정에서 전자 회로는 일반적으로 순수 단결정 반도체 재료로 만들어진 웨이퍼에 점진적으로 생성된다. 규소가 거의 항상 사용되지만, 특수 용도를 위해 다양한 화합물 반도체가 사용된다. 식각 및 포토리소그래피와 같은 단계는 LCD 및 OLED 디스플레이와 같은 다른 장치를 제조하는 데 사용될 수 있다.[1]

제조 공정은 파운드리 또는 "팹"이라고도 불리는 고도로 전문화된 파운드리에서 수행되며,[2] 그 중심부는 "청정실"이다. 최신 14/10/7 nm 노드와 같은 고급 반도체 소자의 경우 제조에 최대 15주가 소요될 수 있으며, 업계 평균은 11~13주이다.[3] 고급 제조 시설의 생산은 완전히 자동화되어 있으며, 자동화된 자재 처리 시스템이 웨이퍼를 기계에서 기계로 운반하는 역할을 담당한다.[4]

하나의 웨이퍼에는 여러 개의 집적 회로가 있으며, 이들은 하나의 웨이퍼에서 잘라낸 조각이므로 다이라고 불린다. 개별 다이는 웨이퍼 절단이라고도 불리는 다이 싱귤레이션 공정을 통해 완성된 웨이퍼에서 분리된다. 그런 다음 다이는 추가 조립 및 패키징 과정을 거칠 수 있다.[5]

제조 공장 내에서 웨이퍼는 FOUP라고 불리는 특수 밀봉 플라스틱 상자 안에 운반된다.[4] 많은 팹의 FOUP에는 내부 질소 분위기가 포함되어 있어[6][7] 웨이퍼 표면의 구리 산화를 방지하는 데 도움이 된다. 구리는 현대 반도체에서 배선에 사용된다.[8] FOUP 및 가공 장비의 내부는 클린룸의 주변 공기보다 깨끗하게 유지된다. 이 내부 분위기는 미니 환경으로 알려져 있으며, 웨이퍼 상의 작동 장치 수인 수율을 향상시키는 데 도움이 된다. 이 미니 환경은 EFEM(장비 프론트 엔드 모듈) 내에 있으며[9] 장비가 FOUP를 수신하고 FOUP에서 장비로 웨이퍼를 도입할 수 있도록 한다. 또한 많은 장비는 오염을 줄이고 공정 제어를 개선하기 위해 깨끗한 질소 또는 진공 환경에서 웨이퍼를 처리한다.[4] 제조 공장은 생산 기계 및 FOUP 내의 분위기를 유지하기 위해 많은 양의 액체 질소를 필요로 하며, 이들은 지속적으로 질소로 퍼지된다.[6][7] 또한 FOUP와 EFEM 사이에 에어 커튼 또는 메시가 있을 수 있으며[10] 이는 FOUP로 유입되는 습기의 양을 줄이고 수율을 향상시키는 데 도움이 된다.[11][12]

산업용 반도체 제조 공정에서 사용되는 기계를 제조하는 회사로는 ASML, 어플라이드 머티어리얼즈, 도쿄 일렉트론, 램 리서치 등이 있다.

Remove ads

특징 크기

요약

관점

특징 크기(또는 공정 크기)는 반도체 제조 공정에서 패턴화할 수 있는 가장 작은 선의 너비로 결정된다. 이 측정값을 선폭이라고 한다.[13][14] 패턴화는 종종 제조 과정에서 장치 설계 또는 패턴을 정의할 수 있는 포토리소그래피를 의미한다.[15] F2는 반도체 제조 공정의 특징 크기를 기반으로 반도체 장치의 여러 부분에 대한 면적 측정값으로 사용된다. 많은 반도체 장치는 셀이라고 불리는 섹션으로 설계되며, 각 셀은 데이터를 저장하는 메모리 셀과 같이 장치의 작은 부분을 나타낸다. 따라서 F2는 이러한 셀 또는 섹션이 차지하는 면적을 측정하는 데 사용된다.[16]

특정 반도체 공정에는 칩의 각 레이어에 대한 최소 크기(너비 또는 CD/임계 치수) 및 간격에 대한 특정 규칙이 있다.[17] 일반적으로 새로운 반도체 공정은 더 작은 최소 크기와 더 좁은 간격을 갖는다. 어떤 경우에는 이를 통해 현재 생산 중인 칩 설계를 단순히 다이 슈링크하여 새로운 설계 비용 없이 비용을 절감하고 성능을 향상시키며[17] 트랜지스터 밀도(단위 면적당 트랜지스터 수)를 증가시킬 수 있다.

초기 반도체 공정은 세대에 대해 임의의 이름(예: HMOS I/II/III/IV 및 CHMOS III/III-E/IV/V)을 가졌다. 나중에 각 새로운 세대 공정은 기술 노드[18] 또는 공정 노드[19][20]로 알려지게 되었으며, 공정의 트랜지스터 게이트 길이의 나노미터(또는 역사적으로 마이크로미터) 단위의 최소 특징 크기로 지정되었다 (예: "90 nm 공정"). 그러나 1994년 이후로는 그렇지 않으며,[21] 공정 노드를 명명하는 데 사용되는 나노미터 수는( 국제 반도체 기술 로드맵 참조) 기능적 특징 크기 또는 트랜지스터 밀도(단위 면적당 트랜지스터 수)와 표준화된 관계가 없는 마케팅 용어가 되었다.[22]

처음에는 트랜지스터 게이트 길이가 공정 노드 이름(예: 350 nm 공정)이 시사하는 것보다 작았지만, 이 추세는 2009년에 역전되었다.[21] 특징 크기는 마케팅에 사용되는 나노미터(nm)와 관련이 없을 수 있다. 예를 들어, 인텔의 이전 10 nm 공정은 실제로 7 nm 너비의 특징( 핀펫 핀의 끝)을 가지고 있어, 인텔 10 nm 공정은 TSMC의 7 nm 공정과 트랜지스터 밀도 면에서 유사하다. 또 다른 예로, 글로벌파운드리스의 12 nm 및 14 nm 공정은 유사한 특징 크기를 갖는다.[23][24][22]

Remove ads

역사

요약

관점

20세기

1955년 벨 전화 연구소에서 일하던 칼 프로슈와 링컨 데릭은 우연히 실리콘 웨이퍼 위에 이산화 규소 층을 성장시켜 표면 부동태화 효과를 관찰했다.[26][27] 1957년까지 프로슈와 데릭은 마스킹과 사전 증착을 사용하여 실리콘 다이옥사이드 트랜지스터를 제조할 수 있었다. 이것은 드레인과 소스가 같은 표면에 인접한 최초의 평면 전계 효과 트랜지스터였다.[28] 벨 랩스에서는 그들의 발견의 중요성이 즉시 인지되었다. 그들의 작업 결과를 설명하는 메모가 1957년 공식 출판되기 전에 벨 랩스에 배포되었다. 쇼클리 반도체 연구소에서는 쇼클리가 1956년 12월에 그들의 기사 예비 인쇄본을 진 호어니를 포함한 모든 고위 직원들에게 배포했다.[29][30][31][32] 그는 나중에 페어차일드 반도체에서 1959년에 평면 공정을 발명했다.[33][34]

1948년 바딘은 반전층이 있는 절연 게이트 트랜지스터(IGFET) 특허를 받았다. 바딘의 개념은 오늘날 MOSFET 기술의 기초를 형성한다.[35] 개선된 유형의 MOSFET 기술인 CMOS는 1963년 페어차일드 반도체에서 치탕 사와 프랭크 완라스에 의해 개발되었다.[36][37] CMOS는 1960년대 후반 RCA에 의해 상업화되었다.[36] RCA는 1968년에 4000 시리즈 집적 회로에 CMOS를 상업적으로 사용하기 시작했으며, 20 µm 공정으로 시작하여 다음 몇 년 동안 점진적으로 10 μm 공정으로 스케일링했다.[38] 많은 초기 반도체 장치 제조업체는 이온 주입기와 같은 자체 장비를 개발하고 제작했다.[39]

1963년 해롤드 M. 매너세비트는 노스아메리칸 항공(현재 보잉)의 오토네틱스 사업부에서 근무하면서 사파이어 위에 실리콘의 에피택셜 성장을 처음으로 기록했다. 1964년 그는 동료 윌리엄 심슨과 함께 저널 오브 어플라이드 피직스에 자신의 연구 결과를 발표했다.[40] 1965년 C.W. 뮬러와 P.H. 로빈슨은 RCA 연구소에서 사파이어 위에 실리콘 공정을 사용하여 MOSFET(금속-산화물-반도체 전계 효과 트랜지스터)를 제작했다.[41]

이후 반도체 소자 제조는 1960년대 텍사스주와 캘리포니아주에서 시작하여 아시아, 유럽, 중동을 포함한 전 세계로 확산되었다.

웨이퍼 크기는 시간이 지남에 따라 1960년 25mm(1인치)에서 1969년 50mm(2인치), 1976년 100mm(4인치), 1981년 125mm(5인치), 1983년 150mm(6인치), 1992년 200mm로 증가했다.[42][43]

2인치 웨이퍼 시대에는 핀셋을 사용하여 수동으로 처리하고 주어진 공정에 필요한 시간 동안 수동으로 고정했다. 핀셋은 웨이퍼를 오염시킬 수 있는 입자를 적게 생성하므로[44] 진공 봉으로 교체되었다. 웨이퍼 캐리어 또는 카세트는 한 번에 여러 웨이퍼를 담을 수 있도록 개발되었지만, 웨이퍼를 개별적으로 캐리어에서 제거하고 처리한 다음 캐리어로 다시 넣어야 했기 때문에, 이 시간을 많이 소모하는 과정을 없애기 위해 내산성 캐리어가 개발되어 웨이퍼가 담긴 전체 카세트를 습식 식각 및 습식 세척 탱크에 담글 수 있게 되었다. 웨이퍼 크기가 100mm로 증가했을 때, 전체 카세트가 균일하게 담가지지 않는 경우가 많았고, 웨이퍼 전체의 결과 품질을 제어하기 어려웠다. 150mm 웨이퍼가 출시될 무렵에는 카세트를 담그지 않고 웨이퍼를 보관하는 웨이퍼 캐리어 및 홀더로만 사용했으며, 웨이퍼를 처리하는 데 로봇이 널리 사용되었다. 200mm 웨이퍼의 경우 웨이퍼 카세트가 더 무거워지므로 수동으로 처리하는 것이 위험해진다.[45]

1970년대와 1980년대에 여러 회사는 반도체 제조 기술을 바이폴라에서 MOSFET 기술로 전환했다. 반도체 제조 장비는 1978년부터 비싸다고 여겨졌다.[46][47][48][49]

1984년 KLA는 최초의 자동 레티클 및 포토마스크 검사 도구를 개발했다.[50] 1985년 KLA는 수동 현미경 검사를 대체하는 실리콘 웨이퍼 자동 검사 도구를 개발했다.[51]

1985년 SGS(현재 ST마이크로일렉트로닉스)는 바이폴라, CMOS 및 DMOS 장치를 사용하는 반도체 제조 공정인 BCD( BCDMOS라고도 함)를 발명했다.[52] 어플라이드 머티어리얼즈는 최초의 실용적인 다중 챔버 또는 클러스터 웨이퍼 처리 도구인 Precision 5000을 개발했다.[53]

1980년대까지는 화학 기상 증착이 등장하기 전까지는 물리 기상 증착이 웨이퍼에 재료를 증착하는 데 주로 사용되는 기술이었다.[54] 확산 펌프를 사용하는 장비는 터보분자 펌프를 사용하는 장비로 교체되었다. 터보분자 펌프는 진공 처리 중 웨이퍼를 오염시키는 오일을 사용하지 않기 때문이다.[55]

200mm 직경 웨이퍼는 1990년에 처음 사용되었으며 2000년에 300mm 직경 웨이퍼가 도입될 때까지 표준으로 사용되었다.[56][57] 브릿지 도구는 150mm 웨이퍼에서 200mm 웨이퍼로의 전환[58] 및 200mm에서 300mm 웨이퍼로의 전환에 사용되었다.[59][60] 반도체 산업은 칩에 대한 수요 증가에 대처하기 위해 더 큰 웨이퍼를 채택했으며, 더 큰 웨이퍼는 웨이퍼당 더 많은 표면적을 제공한다.[61] 시간이 지남에 따라 산업은 FOUP 도입을 가져온 300mm 웨이퍼로 전환했지만,[62] 아날로그 IC, RF 칩, 전력 IC, BCDMOS 및 MEMS 장치와 같이 고급이 아닌 많은 제품은 여전히 200mm 웨이퍼로 생산된다.[63]

클리닝,[64] 이온 주입,[65][66] 에칭,[67] 어닐링[68] 및 산화[69]와 같은 일부 공정은 결과의 재현성을 향상시키기 위해 배치 웨이퍼 처리 대신 단일 웨이퍼 처리를 채택하기 시작했다.[70][71] MEMS 제조에서도 유사한 추세가 존재했다.[72] 1998년 어플라이드 머티어리얼즈는 웨이퍼를 처리하기 위해 챔버가 쌍으로 그룹화되고 공통 진공 및 공급 라인을 공유하지만 그렇지 않으면 격리된 클러스터 도구인 Producer를 도입했다. 이는 격리된 챔버 설계로 인해 품질을 희생하지 않고 다른 클러스터 도구보다 높은 생산성을 제공했기 때문에 당시로서는 혁명적이었다.[73][58]

21세기

오늘날 반도체 산업은 글로벌 사업이다. 선도적인 반도체 제조업체들은 일반적으로 전 세계에 시설을 보유하고 있다. 세계 최대 반도체 제조업체인 삼성전자는 한국과 미국에 시설을 보유하고 있다. 두 번째로 큰 제조업체인 인텔은 미국뿐만 아니라 유럽과 아시아에도 시설을 보유하고 있다. 세계 최대 순수 파운드리인 TSMC는 대만, 중국, 싱가포르 및 미국에 시설을 보유하고 있다. 퀄컴과 브로드컴은 팹리스 반도체 회사 중 가장 큰 회사로, TSMC와 같은 회사에 생산을 위탁한다.[74] 또한 그들은 여러 나라에 시설을 분산 배치하고 있다. 반도체 장치의 평균 활용도가 증가함에 따라 내구성이 문제가 되었고, 제조업체들은 장치가 설계된 시장에 따라 충분한 기간 동안 지속될 수 있도록 장치를 설계하기 시작했다. 이는 특히 10 nm 노드에서 문제가 되었다.[75][76]

SOI 기술은 2001년 이후 생산된 AMD의 130 nm, 90 nm, 65 nm, 45 nm 및 32 nm 단일, 이중, 쿼드, 6 및 8 코어 프로세서에 사용되었다.[77] 2001년 200mm에서 300mm 웨이퍼로 전환하는 동안, 200mm 및 300mm 웨이퍼를 모두 처리할 수 있는 많은 브릿지 도구가 사용되었다.[78] 당시에는 18개의 회사가 최첨단 130nm 공정으로 칩을 제조할 수 있었다.[79]

2006년에는 450mm 웨이퍼가 2012년에 채택될 것으로 예상되었고, 675mm 웨이퍼는 2021년까지 사용될 것으로 예상되었다.[80]

2009년 이후 "노드"는 게이트 길이, 금속 피치 또는 게이트 피치와 관계없이 새로운 세대의 공정 기술을 나타내는 마케팅용 상업적 이름이 되었다.[81][82][83] 예를 들어, 글로벌파운드리스의 7 nm 공정은 인텔의 10 nm 공정과 유사하여, 공정 노드에 대한 전통적인 개념이 모호해졌다.[84] 또한 TSMC와 삼성전자의 10 nm 공정은 인텔의 14 nm 공정보다 트랜지스터 밀도 면에서 약간 더 높을 뿐이다. 이들은 실제로 인텔의 10 nm 공정보다 인텔의 14 nm 공정에 훨씬 더 가깝다 (예: 삼성의 10 nm 공정의 핀 피치는 인텔의 14 nm 공정과 동일하게 42 nm이다).[85][86] 인텔은 10 nm 공정의 이름을 7 nm 공정으로 포지셔닝하기 위해 변경했다.[87] 트랜지스터가 작아질수록 트랜지스터의 자가 발열과 같은 새로운 효과가 설계 결정에 영향을 미치기 시작하며, 16nm 노드 이후로는 전자 이동과 같은 다른 효과가 더욱 명확해졌다.[88][89]

2011년 인텔은 핀펫을 시연했다. 이 핀펫은 게이트가 채널을 3면으로 둘러싸고 있어, 22nm 노드에서 평면 트랜지스터에 비해 에너지 효율성과 게이트 지연을 증가시키고 성능을 향상시킨다. 이는 채널로 한 면만 사용하는 평면 트랜지스터가 단채널 효과로 인해 성능이 저하되기 시작했기 때문이다.[90][91][92][93][94] SuVolta라는 신생 기업은 65 nm 노드에서 매우 가볍게 도핑된 평면 트랜지스터를 사용하는 Deeply Depleted Channel (DDC)이라는 기술을 개발하여 FinFET 트랜지스터와 경쟁했다.[95]

2018년까지 핀펫의 궁극적인 대체재로 여러 트랜지스터 아키텍처가 제안되었으며, 대부분은 GAAFET 개념을 기반으로 했다.[96] 수평 및 수직 나노와이어, 수평 나노시트 트랜지스터[97][98] (삼성전자 MBCFET, 인텔 나노리본), 수직 FET(VFET) 및 기타 수직 트랜지스터,[99][100] 상보형 FET(CFET), 스택형 FET, 수직 TFET, III-V 반도체 재료를 사용한 FinFET(III-V FinFET),[101][102] 나노링, 육각형 와이어, 사각형 와이어, 원형 와이어 게이트-올-어라운드 트랜지스터와 같은 여러 종류의 수평 게이트-올-어라운드 트랜지스터[103] 및 근본적으로 다른 재료를 사용하는 음의 정전용량 FET(NC-FET)가 있다.[104] FD-SOI는 FinFET의 잠재적인 저비용 대안으로 여겨졌다.[105]

2019년 현재, 인텔, UMC, TSMC, 삼성전자, 마이크론, SK하이닉스, 도시바 메모리 및 글로벌파운드리스에 의해 14 nm 공정 및 10 nm 공정 칩이 대량 생산되고 있으며, TSMC와 삼성전자에 의해 7 nm 공정 칩이 대량 생산되고 있지만, 이들의 7 nm 노드 정의는 인텔의 10 nm 공정과 유사하다. 5 nm 공정은 2018년에 삼성에 의해 생산되기 시작했다.[106] 2019년 현재, 가장 높은 트랜지스터 밀도를 가진 노드는 TSMC의 5 나노미터 N5 노드이며,[107] 제곱 밀리미터당 1억 7천 130만 개의 트랜지스터 밀도를 가진다.[108] 2019년에 삼성전자와 TSMC는 3 nm 공정 노드를 생산할 계획을 발표했다. 글로벌파운드리스는 12 나노미터 이후의 새로운 노드 개발을 중단하기로 결정했는데, 이는 12 nm 이하 주문을 처리할 새로운 팹을 건설하는 것이 회사의 재정적 능력을 넘어선다고 판단했기 때문이다.[109]

2020년부터 2023년까지 전 세계적인 칩 부족 사태가 있었다. 코로나19 팬데믹으로 인한 이 부족 기간 동안 많은 반도체 제조업체는 직원들이 회사 부지를 떠나는 것을 금지했다.[110] 많은 국가들이 새로운 제조 공장 또는 팹 건설을 위해 반도체 회사에 보조금을 지급했다. 많은 회사들이 위조 칩의 영향을 받았다.[111] 반도체는 세계 경제와 일부 국가의 국가 안보에 필수적인 요소가 되었다.[112][113][114] 미국은 TSMC에 중국 회사인 화웨이를 위한 반도체를 생산하지 말라고 요청했다.[115] NMOS 및 PMOS 트랜지스터를 서로 위에 쌓는 CFET 트랜지스터가 연구되었다. 이러한 트랜지스터를 구축하기 위해 두 가지 접근 방식이 평가되었다. 단일 공정으로 두 가지 유형의 트랜지스터를 모두 구축하는 모놀리식 접근 방식과 두 가지 유형의 트랜지스터를 별도로 구축한 다음 쌓는 순차적 접근 방식이다.[116]

Remove ads

단계 목록

요약

관점

다음은 현대 전자 장치를 제작하는 동안 여러 번 사용되는 가공 기술 목록이다. 이 목록은 특정 순서를 의미하지 않으며, 모든 기술이 제조 중에 사용되는 것을 의미하지도 않는다. 실제로 순서와 적용되는 기술은 종종 파운드리의 공정 제공 또는 통합 장비 제조 회사(IDM) 자체 제품에 따라 다르며, 반도체 장치에 모든 기술이 필요하지 않을 수 있다. 이러한 공정을 수행하기 위한 장비는 소수의 회사에서 제작한다. 반도체 제조 공장이 가동되기 전에 모든 장비를 테스트해야 한다.[117] 이 공정들은 집적 회로 설계 후에 이루어진다. 반도체 팹은 24시간 연중무휴로 작동하며[118] 많은 팹은 주로 칩 세척을 위해 많은 양의 물을 사용한다.[119]

- 웨이퍼 가공 (프론트 엔드라고도 함)[120]

- 습식 세정

- 부동태화

- 포토리소그래피

- 하드마스크 생성

- 이온 주입 ( 도펀트가 웨이퍼에 삽입되어 전도도가 증가하거나 감소하는 영역을 생성함)

- 에칭 (미세가공)

- 화학기상증착 (CVD)

- 금속유기화학기상증착 (MOCVD), LED에 사용됨

- 원자층 증착 (ALD)

- 물리기상증착 (PVD)

- 스퍼터링

- 증발

- 에피택시[116][128]

- 분자빔 에피택시 (MBE)[129]

- 이온 빔 증착[130]

- 플라즈마 애싱 (완전한 포토레지스트 제거/포토레지스트 스트리핑용, 건식 스트립이라고도 함[131], 역사적으로는 레지스트 스트리퍼라는 화학 용매로 수행됨[132][133], 웨이퍼가 다른 포토리소그래피 라운드를 거칠 수 있도록 함)

- 열처리

- 레이저 리프트오프 (LED 생산용[134])

- 전기화학 증착 (ECD). 전기도금 참조.

- 화학기계적 연마 (CMP)

- 웨이퍼 테스트 ( 자동 시험 장비를 사용하여 전기적 성능을 검증하고, 이 단계에서 분류 및 레이저 트리밍도 수행될 수 있음)

- 다이 준비

- 실리콘 관통 전극 제조 (3차원 집적 회로용)

- 웨이퍼 마운팅 ( 다이싱 테이프를 사용하여 웨이퍼를 금속 프레임에 마운트함)

- 웨이퍼 백그라인딩 및 연마[135] ( 스마트카드 또는 PCMCIA 카드와 같은 얇은 장치 또는 웨이퍼 본딩 및 스태킹을 위해 웨이퍼 두께를 줄임. 이는 웨이퍼 다이싱 중에도 발생할 수 있으며, 이 공정은 Dice Before Grind 또는 DBG[136][137]라고 함)

- 웨이퍼 본딩 및 스태킹 (3차원 집적 회로 및 MEMS용)

- 재배선층 제조 ( WLCSP 패키지용)

- 웨이퍼 범핑 ( 플립칩 BGA (볼 그리드 배열) 및 WLCSP 패키지용)

- 다이 절단 또는 웨이퍼 다이싱

- 집적 회로 패키징

- IC 테스트

또한 라이트 에치와 같은 단계도 수행될 수 있다.

Remove ads

오염 및 결함 방지

특징 너비가 약 10 마이크로미터보다 훨씬 컸을 때, 반도체 순도는 오늘날 장치 제조에서만큼 큰 문제는 아니었다. 1960년대에는 작업자들이 일상복을 입고 반도체 장치를 작업할 수 있었다.[140] 장치가 더욱 통합될수록 청정실은 더욱 깨끗해져야 한다. 오늘날 제조 공장은 가장 작은 입자도 제거하기 위해 여과된 공기로 여압되어 있는데, 이러한 입자는 웨이퍼 위에 떨어져 결함의 원인이 될 수 있기 때문이다. 반도체 청정실의 천장에는 팬 필터 유닛(FFU)이 일정한 간격으로 설치되어 청정실의 공기를 끊임없이 교체하고 여과한다. 반도체 자본 장비는 또한 장비의 EFEM 내에서 공기를 정화하기 위한 자체 FFU를 가질 수 있으며, 이는 장비가 FOUP에 웨이퍼를 받을 수 있도록 한다. FFU는 그릴이 있는 높은 바닥과 결합되어 층류 공기 흐름을 보장하여 입자가 난류로 인해 공중에 떠 있지 않고 즉시 바닥으로 내려가도록 돕는다. 반도체 제조 시설의 작업자들은 인간의 오염으로부터 장치를 보호하기 위해 청정실 슈트를 착용해야 한다.[141] 수율을 높이기 위해 FOUP 및 반도체 자본 장비는 ISO 1등급 먼지 수준의 미니 환경을 가질 수 있으며, FOUP는 더 깨끗한 미세 환경을 가질 수 있다.[12][9] FOUP 및 SMIF 포드는 웨이퍼를 청정실의 공기로부터 격리하여 먼지 입자로 인한 결함 수를 줄여 수율을 높인다. 또한 팹은 청정실 환경을 유지하기 쉽게 하기 위해 청정실에 가능한 한 적은 수의 사람을 배치한다. 왜냐하면 사람들은 청정실 슈트를 입고 있어도 특히 걸을 때 많은 양의 입자를 흘리기 때문이다.[142][141][143]

Remove ads

웨이퍼

일반적인 웨이퍼는 극도로 순수한 실리콘으로 만들어지며, 초크랄스키 공법을 사용하여 직경 300 mm (약 12인치 미만)의 주괴 형태의 단결정 실리콘 실린더로 결정 성장된다. 이 주괴는 약 0.75 mm 두께의 웨이퍼로 절단되고 매우 규칙적이고 평평한 표면을 얻기 위해 연마된다. 생산 공정 중 웨이퍼는 종종 로트(lot)로 그룹화되며, 이는 웨이퍼 캐리어인 FOUP, SMIF 또는 웨이퍼 카세트로 대표된다. FOUP 및 SMIF는 자동화된 OHT(Overhead Hoist Transport) AMHS(Automated Material Handling System)를 통해 팹 내에서 기계와 장비 사이로 운반될 수 있다.[62] SMIF 및 FOUP 외에, 웨이퍼 카세트는 웨이퍼 박스 또는 웨이퍼 운반 박스에 보관될 수 있다.[144]

Remove ads

가공

요약

관점

반도체 소자 제조에서 다양한 가공 단계는 증착, 제거, 패터닝 및 전기적 특성 수정의 네 가지 일반적인 범주로 나뉜다.

- 증착은 재료를 웨이퍼 위에 성장시키거나 코팅하거나 다른 방법으로 옮기는 모든 공정이다. 사용 가능한 기술로는 물리기상증착(PVD), 화학기상증착(CVD), 전기화학 증착(ECD), 분자빔 에피택시(MBE) 및 최근에는 원자층 증착(ALD) 등이 있다. 증착은 산화물 층 형성, 즉 열 산화 또는 더 구체적으로 LOCOS를 포함한다고 이해할 수 있다.

- 제거는 웨이퍼에서 재료를 제거하는 모든 공정이다. 예를 들어 식각 공정(습식 또는 건식)과 화학기계적 연마(CMP)가 있다.

- 패터닝은 증착된 재료의 모양을 만들거나 변경하는 것으로, 일반적으로 포토리소그래피라고 한다. 예를 들어, 재래식 리소그래피에서는 웨이퍼에 포토레지스트라는 화학 물질을 코팅한다. 그런 다음 얼라이너 또는 스테퍼라는 기계가 단파장 빛을 사용하여 웨이퍼에 포토마스크 이미지를 초점화한다. 노출된 영역("양성" 레지스트의 경우)은 현상액 용액으로 씻겨 나간다. 그런 다음 웨이퍼는 식각 과정을 거쳐 마스크로 보호되지 않은 재료가 제거된다. 제거 또는 다른 처리 후, 잔류 포토레지스트는 "건식" 스트리핑/플라즈마 애싱/레지스트 애싱 또는 "습식" 레지스트 스트리퍼 화학 물질로 제거된다.[145] 습식 식각은 1960년대와 1970년대에 널리 사용되었지만,[146][147] 10 마이크론에서 3 마이크론 노드부터는 건식 식각/플라즈마 식각으로 대체되었다.[148][149] 이는 습식 식각이 언더컷(패턴이 있는 마스크 층 또는 레지스트 층 아래를 식각)을 생성하기 때문이다.[150][151][152] 건식 식각은 지배적인 식각 기술이 되었다.[153]

- 전기적 특성 수정은 역사적으로 트랜지스터 소스와 드레인 및 폴리실리콘을 도핑하는 것을 포함했다. 도핑은 반도체 재료의 원자 구조에 불순물을 도입하여 전기적 특성을 수정하는 것으로 구성된다. 처음에는 도펀트를 포함하는 가스와 함께 900-1200°C의 용광로에서 열 확산이 웨이퍼 도핑에 사용되었으며[154][155][156] 이온 주입은 별도의 용광로가 여전히 필요했기 때문에[157] 저항이 있었지만, 1970년대에 이온 주입이 궁극적으로 우세하게 되었다.[158] 이는 칩 제조 중 결과의 재현성을 더 잘 제공하기 때문이다.[39] 그러나 확산은 실리콘 태양 전지 제조에 여전히 사용된다.[159] 이온 주입은 반도체 장치가 이종 원자에 대해 높은 감도를 가지므로 이온 주입이 많은 수의 원자를 증착하지 않기 때문에 실용적이다.[39] 이온 주입을 통한 도핑 공정 후에는 퍼니스 어닐링[160][39] 또는 고급 장치에서는 도펀트를 활성화하기 위해 급속 열 어닐링(RTA)이 이어진다. 어닐링은 처음에는 500~700°C에서 수행되었지만, 나중에는 900~1100°C로 증가했다. 이온 주입 장치는 한 번에 하나의 웨이퍼를 처리하거나, 회전하는 디스크에 최대 17개까지 여러 개의 웨이퍼를 장착하여 처리할 수 있다.[39]

이제 전기적 특성 수정은 UV 처리(UVP)에서 자외선 노출을 통해 저유전율 절연체의 재료의 유전율 감소로도 확장된다. 수정은 종종 산화를 통해 이루어지며, 이는 금속 산화물 전계 효과 트랜지스터를 제조하기 위한 실리콘의 국부 산화와 같은 반도체-절연체 접합을 생성하는 데 사용될 수 있다. 최신 칩은 300개 이상의 순차적인 처리 단계에서 생성된 11개 이상의 금속 레벨을 가질 수 있다.

반도체 제조에서의 레시피는 제조 중 특정 기계가 특정 처리 단계에서 웨이퍼를 처리할 조건을 나열한 것이다.[161] 공정 가변성은 반도체 처리에서 웨이퍼가 균일하게 처리되지 않거나 웨이퍼 표면 전체에서 수행되는 공정의 품질 또는 효율성이 균일하지 않은 경우에 발생하는 문제이다.[162]

FEOL (프론트 엔드 오브 라인) 가공

웨이퍼 가공은 FEOL과 BEOL 단계로 나뉜다. FEOL 가공은 규소에 직접 트랜지스터를 형성하는 것을 의미한다. 원시 웨이퍼는 에피택시를 통해 초고순도, 사실상 결함 없는 실리콘 층을 성장시켜 엔지니어링된다.[163][164] 가장 진보된 로직 소자에서는 실리콘 에피택시 단계 이전에, 구축될 트랜지스터의 성능을 향상시키기 위한 기법이 수행된다. 한 가지 방법은 실리콘-게르마늄(SiGe)과 같은 실리콘 변종을 증착하는 스트레인 단계가 포함된다. 에피택셜 실리콘이 증착되면 결정 격자가 다소 늘어나 전자 이동성이 향상된다. 실리콘 온 인슐레이터 기술이라고 불리는 또 다른 방법은 원시 실리콘 웨이퍼와 후속 실리콘 에피택시의 얇은 층 사이에 절연층을 삽입하는 것을 포함한다. 이 방법은 기생 효과가 감소된 트랜지스터 생성을 초래한다. 반도체 장비에는 증착 및 식각과 같은 공정에서 웨이퍼를 처리하는 여러 챔버가 있을 수 있다. 많은 장비는 공정 제어를 향상시키기 위해 이러한 챔버 사이에서 내부 질소 또는 진공 환경에서 웨이퍼를 처리한다.[4] 화학 용액이 담긴 탱크가 있는 습식 벤치는 역사적으로 웨이퍼 세척 및 식각에 사용되었다.[165]

90nm 노드에서 트랜지스터에 실리콘-게르마늄 영역을 도입하여 PMOS 트랜지스터의 드라이브 전류를 향상시키기 위해 스트레인 엔지니어링으로 제작된 트랜지스터 채널이 도입되었다. 동일한 작업이 20nm 노드에서 NMOS 트랜지스터에서도 수행되었다.[128]

2007년 인텔은 45nm 노드에서 HKMG(고유전율/금속 게이트) 트랜지스터를 도입했는데, 이는 1970년대에 금속 게이트(알루미늄 게이트)[166] 기술을 대체했던 폴리실리콘 게이트를 대체했다.[167] 하프늄 산화물(HfO2)과 같은 고유전율 유전체는 트랜지스터의 대량 누설 전류를 방지하면서 트랜지스터의 지속적인 스케일링 또는 축소를 가능하게 하기 위해 실리콘 산화질화물(SiON)을 대체했다. 그러나 HfO2는 폴리실리콘 게이트와 호환되지 않으므로 금속 게이트를 사용해야 한다. 생산에는 게이트-퍼스트(gate-first)와 게이트-라스트(gate-last)의 두 가지 접근 방식이 사용되었다. 게이트-퍼스트는 고유전율 유전체와 PMOS 또는 NMOS 트랜지스터에 따라 일함수가 달라지는 탄탈륨 질화물과 같은 게이트 금속 증착, 폴리실리콘 증착, 게이트 라인 패터닝, 소스 및 드레인 이온 주입, 도펀트 어닐링, 폴리실리콘 및 소스/드레인 실리콘화를 포함한다.[168][169] DRAM 메모리에서 이 기술은 2015년에 처음 채택되었다.[170]

게이트-라스트는 먼저 고유전율 유전체를 증착하고, 더미 게이트를 생성하며, 이온 증착 및 도펀트 어닐링을 통해 소스 및 드레인을 제조하고, "층간 유전체(ILD)"를 증착한 다음 연마하고, 더미 게이트를 제거하여 트랜지스터가 NMOS인지 PMOS인지에 따라 일함수가 달라지는 금속으로 대체하여 금속 게이트를 생성하는 것으로 구성되었다. 세 번째 공정인 전체 실리콘화(FUSI)[171]는 제조 문제로 인해 추진되지 않았다.[172] 게이트-퍼스트는 22nm/20nm 노드에서 지배적이 되었다.[173][174] HKMG는 평면 트랜지스터에서 핀펫 및 나노시트 트랜지스터에 사용하도록 확장되었다.[175] 하프늄 산화질화물도 하프늄 산화물 대신 사용될 수 있다.[176][4][177][178]

16nm/14nm 노드부터는 원자층 식각(ALE)이 다른 식각 방법보다 높은 정밀도를 제공하기 때문에 식각에 점점 더 많이 사용되고 있다. 생산에서는 플라즈마 ALE가 일반적으로 사용되는데, 이는 재료를 단방향으로 제거하여 수직 벽을 가진 구조를 생성한다. 열 ALE는 모든 방향으로 동시에 재료를 등방성으로 제거하는 데 사용될 수도 있지만, 수직 벽을 생성할 수는 없다. 플라즈마 ALE는 처음에 트랜지스터의 접촉부를 식각하는 데 채택되었으며, 7nm 노드 이후에는 트랜지스터 구조를 식각하여 생성하는 데도 사용된다.[127]

게이트 산화막 및 이식

프론트 엔드 표면 공정 후에는 게이트 유전체(전통적으로 이산화 규소) 성장, 게이트 패터닝, 소스 및 드레인 영역 패터닝, 그리고 원하는 상보적 전기적 특성을 얻기 위한 도펀트의 이식 또는 확산이 이어진다. 동적 램(DRAM) 장치에서는 저장 축전기도 이 시점에 제조되며, 일반적으로 접근 트랜지스터 위에 쌓여 있다 (현재는 없어진 DRAM 제조업체 키몬다는 이 축전기를 실리콘 표면에 깊이 식각된 트렌치로 구현했다).

BEOL (백 엔드 오브 라인) 가공

금속층

다양한 반도체 소자들이 생성되면, 원하는 전기 회로를 형성하기 위해 상호 연결되어야 한다. 이는 BEOL(백 엔드 오브 칩 제조, 즉 패키징 및 테스트 단계와 혼동하지 말 것)이라고 통칭되는 일련의 웨이퍼 처리 단계에서 발생한다. BEOL 처리에는 유전체 층으로 절연된 금속 상호 연결 와이어를 생성하는 것이 포함된다. 절연 재료는 전통적으로 SiO2 또는 실리케이트 유리 형태였지만, 새로운 저유전율 유전체 재료(저유전율 유전체라고도 함)가 사용되고 있으며(예: 실리콘 옥시카바이드), 일반적으로 유전율이 약 2.7(SiO2의 3.82와 비교)이지만, 2.2만큼 낮은 유전율을 가진 재료도 칩 제조업체에 제공되고 있다.

BEoL은 1995년 350nm 및 250nm 노드(0.35 및 0.25 마이크론 노드)에서 사용되기 시작했으며, 동시에 화학적 기계적 연마가 사용되기 시작했다. 당시에는 상호 연결을 위한 2개의 금속층(금속화라고도 함)[179]이 최첨단이었다.[180]

22nm 노드부터 일부 제조업체는 트랜지스터를 BEoL 공정에서 만들어진 나머지 상호 연결에 연결하는 MOL(중간선)이라는 새로운 공정을 추가했다. MOL은 종종 텅스텐을 기반으로 하며 상위 및 하위 층을 가진다. 하위 층은 트랜지스터의 접합부를 연결하고, 상위 층은 트랜지스터를 상호 연결에 연결하는 텅스텐 플러그이다. 인텔은 10nm 노드에서 트랜지스터의 게이트 근처에 트랜지스터 연결용 접촉부를 배치하는 대신 트랜지스터 게이트 위에 직접 배치하여 트랜지스터 밀도를 향상시키는 COAG(contact-over-active-gate)를 도입했다.[181]

인터커넥트

역사적으로 금속 와이어는 알루미늄으로 구성되었다. 이 배선 방식(종종 감산 알루미늄이라고 불림)에서는 먼저 알루미늄 블랭킷 필름을 증착하고, 패턴을 형성한 다음 식각하여 절연된 와이어를 남긴다. 그런 다음 노출된 와이어 위에 유전체 재료를 증착한다. 다양한 금속층은 절연 재료에 구멍("비아"라고 함)을 식각하고 육불화 텅스텐을 사용한 CVD 기술로 텅스텐을 증착하여 상호 연결된다. 이 방식은 동적 램과 같은 많은 메모리 칩 제조에 여전히 사용될 수 있다(그리고 종종 사용된다). 이는 상호 연결 수준이 적을 수 있기 때문이다(4개 이하). 알루미늄은 재결정화를 방지하기 위해 때때로 구리와 합금되었다. 금도 초기 칩의 인터커넥트에 사용되었다.[182]

최근에는 현대 마이크로프로세서에 상호 연결된 트랜지스터 수가 많아져 로직의 상호 연결 수준이 실질적으로 증가함에 따라 배선 지연이 매우 커져 배선 재료(알루미늄에서 구리 인터커넥트 층으로)를 변경해야 했다.[183] 동시에 상호 연결의 유전체 재료(이산화 실리콘에서 새로운 저유전율 절연체로)도 변경되었다.[184][185] 이 성능 향상은 다마신 공정을 통해 비용 절감 효과도 가져오며, 이는 처리 단계를 줄여준다. 상호 연결 수준이 증가함에 따라 후속 리소그래피 이전에 평평한 표면을 보장하기 위해 이전 층의 평면화가 필요하다. 그렇지 않으면 수준이 점점 더 비뚤어져 사용 가능한 리소그래피의 초점 심도를 벗어나 패턴화 능력을 방해할 것이다. CMP(화학기계적 연마)는 이러한 평면화를 달성하기 위한 주요 처리 방법이지만, 상호 연결 수준이 3개 이하일 때는 건식 에치 백이 여전히 때때로 사용된다. 구리 인터커넥트는 구리가 주변으로 확산("오염")되는 것을 방지하기 위해 전기 전도성 장벽층을 사용하며, 종종 탄탈륨 질화물로 만들어진다.[186][181] 1997년 IBM은 최초로 구리 인터커넥트를 채택했다.[187]

2014년 어플라이드 머티어리얼즈는 22nm 노드에서 인터커넥트에 코발트를 사용하는 것을 제안했다. 이는 코발트가 이 응용 분야에서 탄탈륨 질화물보다 더 두꺼울 필요가 있으므로 탄탈륨 질화물을 대체하여 구리 인터커넥트를 코발트로 캡슐화하여 전자 이동을 방지하는 데 사용되었다.[181][188]

Remove ads

웨이퍼 계측

웨이퍼 가공의 고도로 직렬화된 특성은 다양한 가공 단계 사이의 도량형학에 대한 수요를 증가시켰다. 예를 들어, 타원계측법 또는 반사율 측정법에 기반한 박막 계측은 게이트 산화막의 두께뿐만 아니라 포토레지스트 및 기타 코팅의 두께, 굴절률 및 소멸 계수를 엄격하게 제어하는 데 사용된다.[189] 웨이퍼 계측 장비/도구 또는 웨이퍼 검사 도구는 웨이퍼가 테스트까지 이전 처리 단계에서 손상되지 않았는지 확인하는 데 사용된다. 만약 한 웨이퍼에서 너무 많은 다이가 불량인 경우, 추가 처리 비용을 피하기 위해 전체 웨이퍼는 폐기된다. 가상 계측은 물리적 측정 자체를 수행하지 않고 통계적 방법을 기반으로 웨이퍼 속성을 예측하는 데 사용되었다.[2]

장치 테스트

프론트엔드 공정이 완료되면 반도체 소자 또는 칩은 제대로 작동하는지 확인하기 위해 다양한 전기 테스트를 받게 된다. 웨이퍼에서 제대로 작동하는 것으로 확인된 소자의 비율을 수율이라고 한다. 제조업체는 일반적으로 수율에 대해 비밀로 하지만,[190] 이는 30%까지 낮을 수 있는데, 이는 웨이퍼의 칩 중 30%만이 의도한 대로 작동한다는 의미이다. 공정 변동은 낮은 수율의 여러 가지 이유 중 하나이다. 테스트는 불량 칩이 상대적으로 비싼 패키지에 조립되는 것을 방지하기 위해 수행된다.

수율은 종종 장치(다이 또는 칩) 크기와 관련이 있지만 반드시 그렇지는 않다. 예를 들어, 2019년 12월 TSMC는 17.92mm2의 다이 크기를 가진 5 nm 공정 테스트 칩에 대해 평균 약 80%의 수율과 웨이퍼당 최대 90% 이상의 수율을 발표했다. 다이 크기가 100mm2로 증가하면 수율은 32%로 떨어졌다.[191] 다이 크기와 관계없이 웨이퍼의 킬러 결함 수는 일반적으로 cm2 단위의 웨이퍼의 결함 밀도(또는 D0)로 나타낼 수 있다.

팹은 일반적으로 초당 센트 단위의 가격으로 테스트 시간에 대한 비용을 부과한다. 테스트 시간은 몇 밀리초에서 몇 초까지 다양하며, 테스트 소프트웨어는 테스트 시간을 줄이기 위해 최적화된다. 다중 칩(멀티 사이트) 테스트도 가능하다. 많은 테스터가 대부분 또는 모든 테스트를 병렬로 여러 칩에서 동시에 수행할 수 있는 리소스를 가지고 있기 때문이다.

칩은 종종 스캔 체인 또는 "내장 자체시험"과 같은 "테스트 가능성 기능"으로 설계되어 테스트 속도를 높이고 테스트 비용을 줄인다. 특수 아날로그 팹 공정을 사용하는 특정 설계에서는 설계에서 지정한 대로 저항 값을 엄격하게 분산시키기 위해 테스트 중에 웨이퍼도 레이저 트리밍된다.

좋은 설계는 코너(높은 작동 온도와 팹 처리 단계의 극단적인 조합으로 인한 실리콘 동작의 극단적인 경우)를 테스트하고 통계적으로 관리하려고 한다. 대부분의 설계는 최소 64개의 코너를 처리한다.

Remove ads

장치 수율

요약

관점

장치 수율 또는 다이 수율은 웨이퍼의 작동 칩 또는 다이의 수율을 백분율로 나타낸 것이다. 이는 웨이퍼의 칩 수(웨이퍼당 다이 수, DPW)가 칩의 크기와 웨이퍼 직경에 따라 달라질 수 있기 때문이다. 수율 저하는 수율 감소를 의미하는데, 역사적으로는 주로 먼지 입자에 의해 발생했지만, 1990년대 이후로는 주로 공정 변동, 공정 자체 및 칩 제조에 사용되는 도구에 의해 발생한다. 물론 먼지는 많은 오래된 팹에서 여전히 문제로 남아 있다. 먼지 입자는 새로운 공정에서 특징 크기가 축소됨에 따라 수율에 미치는 영향이 증가한다. 자동화 및 생산 장비 내부의 미니 환경, FOUP 및 SMIF 사용은 먼지 입자로 인한 결함 감소를 가능하게 했다. 작동 칩의 판매 가격을 낮추고(작동 칩이 불량 칩의 비용을 지불해야 하므로) 웨이퍼 처리 비용을 줄이기 위해 장치 수율은 높게 유지되어야 한다. 수율은 팹의 설계 및 운영에도 영향을 받을 수 있다.

수율을 높이려면 오염 물질과 생산 공정을 엄격하게 통제해야 한다. 오염 물질은 화학적 오염 물질 또는 먼지 입자일 수 있다. "킬러 결함"은 장치(예: 트랜지스터)의 완전한 고장을 유발하는 먼지 입자로 인한 결함이다. 무해한 결함도 있다. 입자는 킬러 결함을 유발하려면 특징 크기의 1/5 크기여야 한다. 따라서 특징이 100 nm라면 입자는 20 nm만 되어도 킬러 결함을 유발할 수 있다. 정전기도 수율에 부정적인 영향을 미칠 수 있다. 화학적 오염 물질 또는 불순물에는 철, 구리, 니켈, 아연, 크롬, 금, 수은, 은과 같은 중금속, 나트륨, 칼륨, 리튬과 같은 알칼리 금속, 알루미늄, 마그네슘, 칼슘, 염소, 황, 탄소, 불소와 같은 원소가 포함된다. 이러한 원소들이 실리콘과 접촉한 상태로 남아 있지 않는 것이 중요하다. 이는 수율을 감소시킬 수 있기 때문이다. 이러한 원소들을 실리콘에서 제거하기 위해 화학 혼합물이 사용될 수 있으며, 다른 혼합물은 다른 원소에 효과적이다.

수율을 추정하는 데 여러 모델이 사용된다. 머피의 모델, 푸아송의 모델, 이항 모델, 무어의 모델 및 시즈의 모델이 있다. 보편적인 모델은 없으며, 실제 수율 분포(결함 있는 칩의 위치)를 기반으로 모델을 선택해야 한다. 예를 들어, 머피의 모델은 웨이퍼 가장자리에서 수율 손실이 더 많이 발생한다고 가정하고(작동하지 않는 칩이 웨이퍼 가장자리에 집중됨), 푸아송의 모델은 결함 있는 다이가 웨이퍼 전체에 비교적 고르게 퍼져 있다고 가정하며, 시즈의 모델은 결함 있는 다이가 함께 뭉쳐 있다고 가정한다.[192]

작은 다이는 생산 비용이 적게 들고(웨이퍼에 더 많이 들어가고 웨이퍼는 전체적으로 처리되고 가격이 책정되므로), 작은 다이가 웨이퍼 표면적이 적기 때문에 결함이 발생할 가능성이 낮아 더 높은 수율을 달성하는 데 도움이 될 수 있다. 그러나 작은 다이는 큰 다이와 동일한 기능을 수행하거나 능가하기 위해 더 작은 특징이 필요하며, 더 작은 특징은 높은 수율을 유지하기 위해 공정 변동을 줄이고 순도(오염 감소)를 높여야 한다. 도량형학 도구는 생산 공정 중에 웨이퍼를 검사하고 수율을 예측하는 데 사용되므로, 너무 많은 결함이 있을 것으로 예상되는 웨이퍼는 처리 비용을 절감하기 위해 폐기될 수 있다.[190]

다이 준비

일단 테스트가 끝나면 웨이퍼는 일반적으로 "백랩",[120](p. 6) "백피니시", "웨이퍼 백그라인드" 또는 "웨이퍼 박막화"[193]라고도 알려진 공정에서 두께가 줄어든다. 그 다음 웨이퍼는 개별 다이로 스코어링되고 부러지는데, 이 공정을 웨이퍼 다이싱이라고 한다. 양품이고 표시되지 않은 칩만 패키징된다.

패키징

다이의 기능이 테스트되고 분류되면 패키징된다. 플라스틱 또는 세라믹 패키징에는 다이 장착, 다이/본드 패드를 패키지의 핀에 연결하고 다이 밀봉이 포함된다. 미세한 본드 와이어는 패드를 핀에 연결하는 데 사용된다. '옛날'(1970년대)에는 와이어가 손으로 부착되었지만, 지금은 전문 기계가 이 작업을 수행한다. 전통적으로 이 와이어는 금으로 구성되어 납땜으로 도금된 구리의 리드 프레임 (발음 "리드 프레임")으로 이어졌다. 납은 유독하므로 RoHS에 따라 무연 "리드 프레임"이 현재 의무화되었다. 전통적으로 본드 패드는 다이의 가장자리에 위치하지만, 플립칩 패키징은 다이 전체 표면에 본드 패드를 배치하는 데 사용될 수 있다.

칩 스케일 패키지 (CSP)는 또 다른 패키징 기술이다. 플라스틱 이중 직렬 패키지는 대부분의 패키지와 마찬가지로 내부에 숨겨진 실제 다이보다 몇 배 더 크지만, CSP 칩은 다이 크기와 거의 같다. CSP는 웨이퍼가 다이싱되기 전에 각 다이에 대해 구성될 수 있다.

패키징된 칩은 패키징 중에 손상되지 않았는지, 그리고 다이-핀 연결 작업이 올바르게 수행되었는지 확인하기 위해 다시 테스트된다. 그런 다음 레이저가 칩의 이름과 숫자를 패키지에 식각한다. 다이의 테스트 및 패키징, 그리고 완성된 패키징 칩의 최종 테스트를 포함하는 단계를 백엔드,[120] 포스트-팹,[194] ATMP(Assembly, Test, Marking, and Packaging)[195] 또는 ATP(Assembly, Test and Packaging)라고 부르며, 반도체 파운드리와는 별개인 OSAT(OutSourced Assembly and Test) 회사에서 수행할 수 있다. 파운드리는 반도체 제조의 프론트엔드에 속하는 포토리소그래피 및 식각과 같은 제조 공정을 수행하는 회사 또는 팹이다.[196]

Remove ads

위험 물질

제조 공정에는 많은 독성 물질이 사용된다.[197] 여기에는 다음이 포함된다.

- 비소, 안티모니, 인과 같은 독성 원소 도펀트.

- 이온 주입 도핑에 사용되는 비소와 인을 각각 포함하는 아르신 및 포스핀, 트랜지스터 인터커넥트에서 텅스텐의 CVD 증착에 사용되는 육불화 텅스텐, 폴리실리콘 증착에 사용되는 실레인[198], 실리콘 태양광 전지용 고순도 폴리실리콘 또는 초크랄스키 공법으로 단결정 실리콘 웨이퍼를 만드는 폴리실리콘을 생성하는 데 사용되는 트라이클로로실레인[199][200], 또는 실리콘 필름 증착에 사용되는 트라이클로로실레인[201]

- 식각 및 세척에 사용되는 과산화 수소, 발연 질산, 황산 및 플루오린화 수소산과 같은 고반응성 액체.

작업자들이 이러한 위험한 물질에 직접 노출되지 않도록 하는 것이 중요하다. IC 제조 산업에서 흔히 볼 수 있는 높은 수준의 자동화는 노출 위험을 줄이는 데 도움이 된다. 대부분의 제조 시설은 습식 스크러버, 연소기, 가열 흡착 카트리지 등과 같은 배기 관리 시스템을 사용하여[202][203][204] 작업자와 환경에 대한 위험을 통제한다.

상용 MOSFET 노드 타임라인

같이 보기

- 데스니움

- 마이크로일렉트로닉스 제조 용어집

- 반도체 스케일 예시 목록

- MOSFET

- 멀티게이트 소자

- 반도체 산업

- 파운드리 모델

- 반도체 장비 판매 선두 기업 연도별

- 국제 반도체 기술 로드맵

- 반도체 통합

- 실리콘의 국부 산화 (LOCOS)

- 집적 회로 제조업체 목록

- 반도체 제조 공장 목록

- 미세가공

- 반도체 장비 및 재료 국제 협회 (SEMI) - 반도체 산업 무역 협회

- SEMI 폰트 웨이퍼 라벨용

- 에치 피트 밀도

- 부동태화

- 평면 공정

- 트랜지스터 수

각주

추가 자료

외부 링크

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads