トップQs

タイムライン

チャット

視点

PCI Express

シリアルインタフェース、拡張バス ウィキペディアから

Remove ads

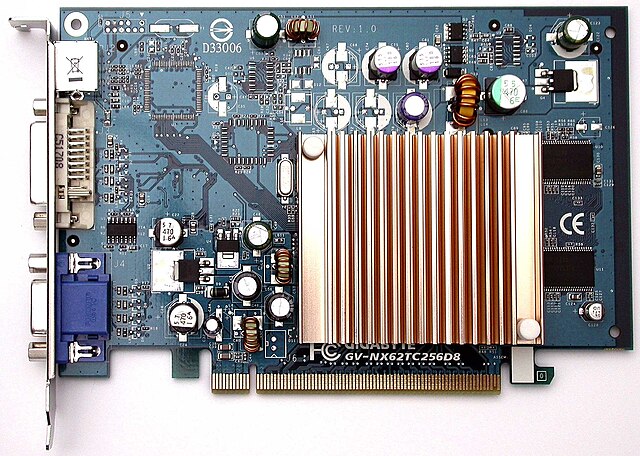

PCI Express(ピーシーアイエクスプレス)は、2002年にPCI-SIGによって策定された、I/Oシリアルインタフェース、拡張バスの一種である。書籍、文書ではPCIeと表記されることも多い。この表記はPCI-SIG自身もウェブサイト上で使用している。PCI-Xはパラレルインタフェースの別規格である。

Remove ads

概要

PCIバス、およびPCI-Xバスの欠点を補うべくインテルが開発を進めていた3rd. Generation I/O、3GIO(スリージーアイオー)を基とする。

PCI Express 1.1は、1レーンあたり2.5 Gbpsでデータ転送に80パーセントが使用され、送信/受信を分離した全二重方式を採用し、計5 Gbpsの転送速度を持つ[2]。これは従来の32ビット/33 MHzのPCIバスに比して3倍から4倍に迫り、AGP 2xモードのそれに近い。高度な3D描画処理を行わないビデオカードならばx1モードでも充分な転送速度を確保できる。またレーンを複数束ね、高転送速度を可能とするx2、x4、x8、x16、x32も仕様化されている[2]。特にPCI Express x16は、バススロットに用いるコネクタの物理的長さが従来のAGPやPCIに近く、AGPに代わるビデオカードのインタフェースとして利用されている。転送速度は8 GB/s(2.5 Gbps時、送受信それぞれ4 GB/s)で、AGP 8xモード比でおよそ4倍弱となる。

PCI Express x1をベースとした新たなPCカード規格ExpressCardはノートパソコンなどに採用される。ノートパソコンなどで内蔵の無線LANボード用に多く採用されるmini PCI Express端子はPCI Express (x1) とUSB 2.0の信号配線がある。mSATA端子と端子形状は同一だが信号線の互換性はない。

Remove ads

リビジョンと転送速度

要約

視点

PCI Express 1.1 (Gen1)

2005年にPCI-SIGが発表した[3]。それ以前の2002年に1.0が策定されたものの、そのままでは通信ができないという致命的な不具合が存在しており、これを修正した1.0aが2003年に発表され、2005年にわずかな変更を加えたものとして策定された[3]。

伝送路1レーンあたりの物理レイヤの帯域は片方向2.5 Gbpsで双方向で5.0 Gbpsだが、実効データ8ビットの送信に物理レイヤ上で2ビットの同期制御ビットを加える8b/10bエンコード方式を用いており、実効データ転送速度は片方向250 MB/sで双方向500 MB/sになる[2]。伝送路のレーンを束ねることでポートのデータ転送速度向上が可能である[2]。束ねるレーン数によってそれぞれx1、x2、x4、x8、x12、x16、x32と表す[2]。レーンを16束ねたPCI-E 1.1 x16の通信ポートの実効データ転送速度は、片方向4 GB/s、双方向では8 GB/sになる。

PCI Express 2.0 (Gen2)

速度をPCI Express 1.1の2倍に引き上げ、1レーンあたりの物理帯域は片方向5.0 Gbpsで実効データ転送速度は片方向500 MB/sで双方向1 GB/sである[4]。

Intelのコンシューマ向けプラットフォームでは2007年発売のX38チップセット[5]と翌2008年の4シリーズチップセット[6]にて、AMDにおいては2008年発売の700シリーズチップセット[7]にて対応。

PCI Express 3.0 (Gen3)

2010年11月18日にPCI-SIGが制定した[8]。

当初は1レーンあたりの物理帯域10 Gbpsを目標としたが技術的困難から8 Gbpsに改め、エンコード方式を128b/130bに変更して転送効率を向上させた[3][9]。PCI Express 3.0は従来の1.1や2.0の機器とも接続互換性を有する[8]。実効データ転送速度は当初目標のPCI Express 2.0比約2倍となり、1レーンあたりの実効データ転送速度は片方向0.9846 GB/sで双方向1.969 GB/sとなった。PCI Express 3.0のポートは規格上最大32レーンまで束ねられ、1ポートの最大の実効データ転送レートは片方向31.51 GB/s、双方向63.02 GB/sである。PCI Express 3.0以降は#物理レイヤの帯域をギガビット毎秒 (Gbps) でなくギガトランスファ毎秒 (GT/s) で表記することが多くなった。

Intelは2012年発売のIvy Bridge世代のCPUで正式対応[10]。ただし主にビデオカード向けの拡張スロットで利用されるCPUが提供するレーン (x16)に限られ、他の拡張スロットやオンボードデバイスに用いられるチップセットが提供するレーンが対応したのは2015年発売のSkylakeに対応した100シリーズからとなる。AMDは2014年のKaveri世代で対応[11]。ただしこれはAPUであり、より高性能なCPUでは2017年のRyzenにて対応[12]。

PCI Express 4.0 (Gen4)

2017年10月に策定、公開[13]。策定に時間がかかり、Gen3の策定から7年かかっている。

1レーンあたりの物理帯域をPCI Express 3.0 (Gen3) の2倍に引き上げて片方向16 GT/sとする[13]。

単純に高速化しただけではバスを活かしきれない可能性があったため、パケットヘッダのタグが256個から768個へ拡張され、それらを効率的に扱うためのクレジットのスケーリング機能 (クレジットを1倍/4倍/16倍として扱う機能) が追加された。

AMDは2019年発売のZen 2世代のCPUで対応[14]。同時発表されたハイエンド向けのX570チップセットもそれまでの2.0から3.0をスキップして4.0に対応している。Intelは2020年発売のComet Lake世代までは対応していないものの、同時に発売されたLGA1200ソケットのマザーボードの一部が独自に対応しており[15][16]、後継のRocket Lakeで正式対応となった[17]ほか、チップセットでも翌2021年の600シリーズから対応している[18]。AMDのチップセットでの対応は2019年 - 2020年発売の500番台チップセットからとなる。

PCI Express 5.0 (Gen5)

2017年6月7日にPCI-SIGが発表。2019年5月29日の策定完了を発表[19][20]。

PCI Express 3.0 (Gen3) の4倍、PCI Express 4.0 (Gen4) の2倍の速度である片方向32 GT/sを実現する[13]。

バスの速度は通常2.5 GT/s、8 GT/s、16 GT/s、32 GT/sの順に引き上げられていくが、切り替え毎に100 ms(32 GT/sに達するまで計300 ms)を要するため中間速度をバイパスして2.5 GT/sから32 GT/sへ直接切り替える (100 msに短縮される) 機能が追加された。この場合、中間速度は使用されず2.5 GT/s、5 GT/s、32 GT/sのみの動作となる。

電源コネクタの規格として12vHPWRが設定された[21]。

Intelは2021年発売のAlder Lakeから対応[22]。AMDではZen 4から対応。コストや対応製品の少なさ[注 2]から、Intelはビデオカード向けのx16のみ、AMDはCPUの提供するレーンであってもチップセットによってGen5への対応が異なる。

PCI Express 6.0 (Gen6)

2019年6月18日にPCI-SIGが発表[23]。2022年1月11日の策定完了を発表[24]。

PCI Express 4.0 (Gen4) の4倍、PCI Express 5.0 (Gen5) の2倍の速度である片方向64 GT/sを実現する[25]。

エンコード方式は従来のNRZ 128b/130bからPAM-4 242B/256Bに変更され、PCI Express 5.0 (Gen5) と同じバスクロックのまま転送速度が約2倍になる。配線可能な距離はPCI Express 5.0 (Gen5) と同程度となる。

PCI Express 7.0 (Gen7)

2022年6月22日にPCI-SIGが発表[26]。2025年に策定予定と発表[24][27]。

PCI Express 6.0 (Gen6) の2倍の速度である片方向128 GT/sを実現する[28]。

2025年6月11日、PCI Express 7.0の仕様が正式に公開された[29]。

PCI Express 8.0 (Gen8)

2025年8月7日にPCI-SIGが発表。2028年に策定予定と発表[30]。

PCI Express 7.0 (Gen7) の2倍の速度である片方向256 GT/sを実現する。

転送速度

Remove ads

開発から普及までの経緯

要約

視点

パラレル・インタフェースの問題点

PCIバスなどのパラレルインタフェースでデータ転送速度の向上は、

- バス幅を拡幅してデータ線を増加

- 単位時間あたりの転送回数の増加を企図して高クロック化

が奏功する。PCIバスは当初の32ビット/33 MHz (133 MB/s) から64ビット/66 MHz (533 MB/s) までデータ転送速度が引き上げられた。PCI-Xバスは、バスクロックのDDR/QDR化も含め64ビット/1066 MHz相当まで仕様化されている。

上記手法の高速化は限界がある。バス幅の拡大はデータ線の増加、LSIのピン増加、として製造コスト上昇の要因となる。クロックの高速化はデータとクロックタイミングを一致させるため、LSIとボードの設計と製造に高度技術が求められてコストが増加する。PCI-Xは厳密な設計が要求されるため民生品の商品化は価格面で困難で、パーソナルコンピュータまで普及しなかった。

かつては製造コストに比して性能が上昇したが、高速化の限界を迎えてインテルはメインメモリインターフェイスのシリアル化を提唱した。

PCIバスの限界

PCIバス登場当初から一貫してパーソナルコンピュータ市場で広く普及しているPCIバスのモードは、32ビット/33 MHzだった。バス伝送帯域は主にビデオカードが消費していたがAGPによって事実上隔離されており、PCIバスは安泰であった。チップセット内部ないしはブリッジチップでPCIバスに接続されるハードディスクのインタフェースのIDEは、サポートする転送速度を次第に引き上げて2000年に66 MB/s、2002年に100 MB/sの転送速度をサポートした。ハードディスクの転送速度は追いついていなかったが、民生品市場におけるRAIDの流行、その他、高性能なビデオ編集用拡張カードの普及、PCIバスに接続されるギガビットLANの1000BASE-Tをサポートする拡張カードの登場など、バス帯域を消費するデバイスの普及が始まり、ユーザは転送速度向上を望むようになった。

シリアル・インタフェースの台頭

1本の信号線と付随して基準線とするアース線でデータ伝送を行うシリアルインタフェースはRS-232Cが知られる。パリティビットによる簡易な誤り検出訂正しか物理層に組み込めず、誤り訂正が増加する高速データ転送に不向きとされていた。

パラレルデータにクロックを埋め込みシリアル・データ化する8b/10b技術をIBMが開発し、シリアル転送が再び着目された。イーサネットで採用されて普及が広まると8b/10b機能を搭載したSERDESチップの価格が低下し、ファイバーチャネルやギガビットイーサネット (GbE) で転送速度も高速化された。

PCI Expressの登場

I/Oインタフェースの転送速度不足解消のために次世代インタフェースを模索していたインテルは、シリアルインタフェースであるNGIO (Next Generation I/O) の開発を開始し、ヒューレット・パッカードやIBMも、PCIバスに代わるI/OインタフェースとしてFuture I/Oと呼ばれるシリアル・インタフェースを開発していた。

両者は後に統合されてInfiniBandとなったがソフトウェアレベルでPCIバスと互換性を有さず、マイクロソフトなどもサポートに消極的で、現在[いつ?]スーパーコンピュータのノード間接続など低遅延で高スループットな要求分野で利用される。

インテルはこの失敗を教訓として3GIO (Third Generation I/O) の開発を開始した。ソフトウェア・レベルでPCIバス完全互換とし、正統なPCIバスの後継者とすべくPCI ExpressとしてPCI-SIGでの仕様化が行われた。

ソフトウェアの対応

PCI Expressは従来のPCIと互換性があるため、PCIバスをサポートするオペレーティングシステム (OS)には、特に変更は必要ない。この場合PCI ExpressデバイスはPCIデバイスとして操作される。

普及

パーソナルコンピュータ向けマザーボードへの実装は比較的早くに行われた。主に搭載されるのはx16とx1である。

転送速度が何よりも要求されるビデオカードでは特に歓迎され、2005年頃にAGPからの置き換えがほぼ完了し、2022年現在ではハイエンドからローエンドまでPCI Express x16が主流となった。

マザーボード市場でAGPスロットを有する製品は、2022年現在組み込み向けなどの特殊な用途を除けばほとんど存在しない。汎用バスとしてのPCIスロットも、一般用途のマザーボードにおいて搭載している製品は少数である。サーバ向けマザーボードは依然として64ビットPCIやPCI-Xを実装したものも多い。

ATAカードをはじめとしたインタフェースカード類は比較的早くから PCI Express (x1) に移行しており、ビデオキャプチャ、テレビチューナ、サウンドカードなどマルチメディア関連商品はPCI Express対応が多い。旧来システムのアップグレードパスとしてモデルチェンジを行わず販売を継続しているPCI製品もある。2016年時点でATXマザーボードの拡張スロットはPCI Express x16、x1、PCIの3種類を採用したものが多く、PCIの需要よりチップセット側のPCI Expressの総帯域制限によるものが多い。その後更に移行が進み、2020年代にはPCIスロットを持つものはほとんどなくなった。PCI Expressの柔軟性を活かし、x16形状のスロット2本をそれぞれx8接続、あるいは片方をx16にし片方を無効にするといった設定ができるものがある。また形状はx16なものの、信号線をx4のみ配線する、あるいは逆にx4のスロットの端を切り欠き、x8以上の長いカードを挿せるようになっている実装も登場している。オンボードデバイスは、従来PCIバスを用いて接続していた物を完全にPCI Express接続に置き換えたマザーボードが大半である。IntelはP67以降のメインストリーム向けチップセットからPCIをサポートしておらず、別途ブリッジチップを用いてPCI Express経由で接続している。2012年後半からPCI Express 3.0仕様に対応したマザーボードやビデオカードが発売された。

シングルボードコンピュータにあっては、SoC内部のバスからブリッジを経由してPCI Expressをサポートした製品が存在する。例として、Raspberry Pi 4 Model BではBCM2711内部のAXIバスからブリッジを経由してPCI Expressバスを引き出し、その先にXHCIを接続することによりUSB 3.0をサポートしている。一方で、デバイスから独立したDMAコントローラの搭載が難しい[注 3]などSoC特有の問題が解決しにくいことから、オンチップバスとしてPCI Expressを採用した例は少ない。

Remove ads

仕様

要約

視点

データ転送方式はPCIバスのハンドシェークと異なり、ネットワークでパケット送受信される。アーキテクチャはレイヤ構造を有し、トランザクション・レイヤ、データリンク・レイヤ、物理レイヤの3層構造となっている。

送信では、CPUや他デバイスから発行されたリクエストは、トランザクション・レイヤで上位のソフトウェア層に対してPCIと互換性のある機能を提供するパケットを付加され、データリンク・レイヤに渡される。データリンク・レイヤーは、接続されている相手側デバイス間との送受信の制御を担っており、パケットにシーケンス番号、CRCを付加して物理レイヤに渡す。物理レイヤはシリアル転送を受け持つ部分で、Gen1, 2では8b/10b変換、Gen3では128b/130b変換などを行い、SERDESによりパケットがシリアル・データとして送られる。

また、トポロジは、従来のPCIのマルチ・ドロップ型ではなく、ポイント・ツー・ポイント接続である。ポートの拡張はスイッチを必要とする。

トランザクション・レイヤ

トランザクション・レイヤは主にトランザクション・レイヤ・パケット (Transaction Layer Packet : TLP) の生成と復号を担う。TLPはリードやライトといったコマンドやアドレス、データなどから構成される。トランザクション・レイヤは接続相手とのフロー制御も行う。PCI Expressのフロー制御はクレジット・ベースで行われ、予め自分が受信することの出来るバッファのサイズを相手に通知し、バッファに空きが出来るたびに伝える方式である。送信側は自身が送信したパケットのサイズを積算し、送信相手からバッファの空きが伝えられるとその分を減算することで、送信相手のバッファ・サイズを超えることなくパケットの転送が可能となる。

トランザクション・レイヤはパケットを任意のサイズに分割する機能を有する。一つのTLPで最大4キロバイトのメモリ・リードを発行することが可能であるが、メモリから4キロバイトを一度で読むことは都合が悪い場合がある。メモリ・リードでキャッシュ・コヒーレンシを維持するシステムの場合、CPUに対しキャッシュに最新データの有無を問い合わせる。インテル系の32ビットCPUはキャッシュ・ライン・サイズは64バイトで、4キロバイトのメモリ・リードは全て64バイトの64個のメモリ・リードに分割される必要がある。トランザクション・レイヤは自デバイス内で、都合良くパケットを分割する。1つのRead requestのデータを返す時に複数のcompletionに分割して返すこともできるが、返すデータの順序は入れ換えられない。

トランザクション・レイヤは以下の4個のアドレス空間をサポートする。

- Memory 空間

- I/O 空間

- Configuration 空間

- Message 空間

前者3空間はPCIバス互換の空間である。Message空間は、従来サイドバンド信号で通知を行っていたもので、割り込み、電源制御などの通知に使用される。

データリンク・レイヤ

データリンク・レイヤは、トランザクション・レイヤと物理レイヤの中間に位置し、主にPCI Expressリンクの管理、エラー検出と訂正を担う。

送信側データリンク・レイヤは、トランザクション・レイヤから渡されたTLPをバイナリ値としてデータを保護するためのCRCを算出し、TLPの授受を確認するためのシーケンス・ナンバをTLPに付加して物理レイヤに渡す。受信側はCRCによるデータ化けチェックと、シーケンス・ナンバによるパケット欠落チェックを行う。

受信側でエラーを見つけた場合、送信側に再送を促すためにNAK (Not Acknowledge) パケットをエラー検出したTLPのシーケンス・ナンバと共に送信側に返す。正常にTLPを受信した場合は、同様にACK (Acknowledge) パケットを返す。

エラーによるパケットの再送機能もデータリンク・レイヤが受け持っており、NAKを受信した場合そのシーケンス・ナンバから全て送信し直すため、データリンク・レイヤ内に再送バッファが実装される。

データリンク・レイヤは、TLPの送受信の他にもDLLP (Data Link Layer Packet) と呼ばれるデータリンク・レイヤ同士でのみ情報を交換するパケットも送受信する。ACK、NACKパケットや、フロー制御に使用するバッファ・サイズ通知などもDLLPが使用される。

物理レイヤ

物理レイヤは入出力バッファの制御回路、シリアル-パラレル/パラレル-シリアル変換回路、PLL、インピーダンス調整回路などで構成される。

PCI Express 1.1の物理メディアは2線、800 mV差動で400 ps単位でデータのドライブされる。送信、受信専用の信号を必要とする全二重方式で、x1の場合に実際は4本の信号が使用される。

PCI Express 1.1までは2.5 GT/sでデータ転送しているが、PCI Express 2.0は5.0GT/sで転送している。PCI Expressをケーブルで接続するための仕様検討も行われている。

物理レイヤは将来的により高速なメディアに置き換えられることから、物理レイヤとデータリンクレイヤ間のインタフェースは特に規定されておらず各ベンダの実装に依存している。

物理形状

PCI Express Card Electromechanical Specificationとして拡張カードの電気および物理形状が規定され、カードエッジを含むコネクタの仕様も規定される。スロットの色については標準化されていないため、マザーボードのメーカーにより異なる[31]。対応するリビジョンで色分けする例もあるが[32]、その意味するところは説明書に記述するかボード上の印刷で明示しなければユーザーには判別できない。材質は基本的にプラスチック類であるが、大型のビデオカードを想定し金属を採用した例もある[33]。

ロープロファイルPCI Express

→「ロープロファイルPCI」も参照

ロープロファイルPCI Expressはカードの物理形状がPCI Expressより小さい。

ピンアサイン

下記の表に PCI Express カードに設けられたエッジ・コネクタにおける接点(ピン)とその役割を示す。プリント基板 のうちはんだ面を A サイド、部品面を B サイドと表記する。[34] PRSNT1# 及び PRSNT2# ピンは他のピンに比べて若干短く、ホットスワップ による装着を行う際他のピンに遅れて最後に接触することが意図されている。WAKE# ピンの駆動はホストコンピュータをローパワー状態から復帰させる(Wake Up)が、Wake Up 可能であることを示すため、当ピンは予めスタンバイ電源によりプルアップしておく必要がある。[35]

- Reserved for future second PCI Express Lane (if needed)

- Reserved for future Subscriber Identity Module (SIM) interface (if needed)

- Reserved for future wireless disable signal (if needed)

- Reserved for future wireless coexistence control interface (if needed)

電力供給

スロットからの最大供給電力を超えるカードについては、下記のとおりATX12V Ver2.xの補助電源プラグを併用する。

Remove ads

欠点

相互接続性の問題

PCIバスは32ビットバスのデバイス/スロットと64ビットバスのデバイス/スロットの全ての組み合わせで動作が保証されていたが、PCI Expressはx16仕様のカードをx8仕様のスロットに挿入できない[注 4]。マザーボードにはx1/x4/x8コネクタのエッジに初めから切り欠きを設け、x16仕様カードを挿入可能な「エッジフリー」と称する製品もあるが、カード端子の物理的保護などの問題点は解消されないマザーボードもある(例えばIntel DX58S0)。

解決事例として、AppleのMac ProやIntel 3シリーズ以降、AMD 7シリーズのマルチGPU対応チップセット搭載マザーボードが採用した実装などがある。後述の利点を参照。

供給電力の不足

x16で75Wの供給に対応しているが、主な用途であるビデオカードにおいては2005年発売のGeForce 7シリーズから75W以上を消費する製品が登場しており、2008年のGeForce 200シリーズでは補助電源プラグの使用が開始された。以降のビデオカードは補助電源を前提とした設計となっているなど[42]、ビデオカードは挿入しただけで使えない製品が主流であり、逆に「補助電源不要」をアピールした製品が販売されている[43]。75Wで動作するが補助電源プラグを搭載し、併用するとオーバークロックが可能になる製品も存在する[44]。その後もビデオカードの消費電力が増大し続け従来の6ピン(75W)や8ピン(150W)のコネクタでは供給が追いつかなくなったことから、PCI Express 5.0にて16ピンで最大600Wを供給可能な「12vHPWR」が追加された[21]。

重量物

規格ではボードの4辺の内、スロットと筐体外部側の2カ所で支えるようになっているが、2020年ごろからハイエンドモデルのビデオカードはヒートシンクやヒートパイプなどの冷却装置が大型化したことで重量が1.8kgに達する製品も販売され、支えられていない側が垂れ下がる[45]、取り外す際にスロットのロックが破損するなどの事例が報告されるようになった[46]。規格ではこのような重量物を支えることを想定していないため、金属製のスロットを採用したマザーボードやビデオカードを支える器具が登場している[45]。対策としてハイエンドモデルのビデオカードには、金属製のプレートを基板の裏に配置し反りを防ぐことをアピールした製品もある[47]。

Remove ads

利点

PCI Expressの利点の一つとしてレーン数のフレキシビリティが挙げられる。カードエッジコネクタがx16形状でもx1モードで規格上は動作可能で、上位の長いスロットに下位の短いカードエッジコネクタは挿入可能である。BIOS上もしくはOS上から、チップセットのサポートレーン数を上限としてユーザーが任意に設定する設計も可能である。

合計レーン数の上限を26として4つのx16用物理スロットに対し

- x8 x1 x1 x16(余り0)

- x4 x4 x1 x16(余り1)

- x8 x1 x8 x8(余り1)

- x4 x4 x8 x8(余り2)

と複数の振り分け選択も可能である。余剰レーンの未使用による不利益は無い。x16モードで動作するスロットにx1専用カードを挿入しても問題なく動作する。

スロットコネクタの物理規格は、スロットに割り振り可能な規格上のレーン数上限を示す。マザーボード設計者は、使用するチップセットのサポートレーン数の範囲内で、スロット本数と与えるレーン数の設計が可能である。

Remove ads

脚注

参考文献

関連項目

外部リンク

Wikiwand - on

Seamless Wikipedia browsing. On steroids.

Remove ads